上拉电阻和下拉电阻的选型和计算

常见各类技术资料上,有些技术规范写道"无用的管脚不允许悬空状态,必须接上拉或下拉电阻以提供确定的工作状态"。

这个提法基本是对的,但也不全对。下面详细加以说明。

管脚上拉下拉电阻设计出发点有两个:

一个是在正常工作或单一故障状态下,管脚均不应出现不定状态,如接头脱落后导致的管脚悬空;

二是从功耗的角度考虑,就是在长时间的管脚等待状态下,管脚端口的电阻上不应消耗太多电流,尤其是对电池供电设备。

从抗扰的角度,信号端口优选上拉电阻。上拉电阻时,在待机状态下,源端输入常为高阻态,如果没有上拉电阻或下拉电阻,输入导线呈现天线效应,一旦管脚受到辐射干扰,管脚输入状态极容易被感应发生变化。所以,这个电阻是肯定要加的。下一个问题就是加上拉还是下拉。

如果加了下拉,在平常状态下,输入表现为低电平,但辐射干扰进来后,会通过下拉电阻泻放到地,就会发生从Low—High的一个跳变,产生误触发。相当于一个乞丐,你给了他10万元,他的生活方式就会从穷人到富人发生一个改变。

但如果加了上拉电阻,在平常状态下,输入表现为高电平,辐射干扰进来后,如果低也没关系,上拉电阻会将输入端钳位在高电平,如果辐射干扰强,超过了Vcc的电平,导线上的高电平干扰会通过上拉电阻泻放到Vcc上去,无论怎样干扰,都只会发生High—Higher的变化,不会产生误触发。相当于人家本来是一个富豪,你给了他10万元,他的生活方式不会发生任何的改变。

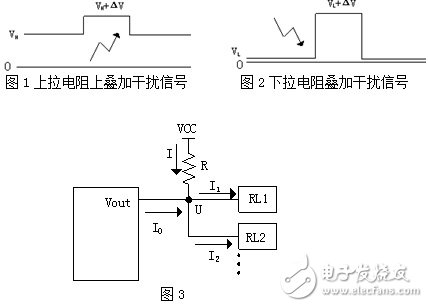

图1和图2是干扰状态下的电平示意图。图2中的低电平由VL变为VL+ΔV时,产生了从低电平到高电平的跳变,有可能使后级电路误动作的风险。

下一个问题就是,确定了用上拉电阻后,是不是上拉电阻就可以随便选了呢?答案当然是"no"。(如图3)

在前极输出高电平时,Vout输出电流,U为高电平。有两种情况:

A、当I0 >= I1 + I2

这种情况下,RL1和RL2两个负载不会通过R取电流,因此对R阻值大小要求不高,通常4.7 KΩ<R<20 KΩ即可。此时R的主要作用是增加信号可靠性,当Vout连线松动或脱落时,抑制电路产生鞭状天线效应吸收干扰。

B、当I0 <I1 + I2

I0 +I= I1 + I2

U=VCC-IR

U>=VHmin

由以上三式计算得出,R<=(VCC- VHmin)/I

其中,I0、I1、I2都是可以从datasheet查到的,I就可以求出来,VHmin也是可以查到的。

当前极Vout输出低电平时,各管脚均为灌电流,则:

I’= I1’ + I2’ +I0’

U’ =VCC-I’ R

U’ <=VLmax

以上三式可以得出:R>=(VCC- VLmax)/I’

由以上二式计算出R的上限值和下限值,从中取一个较靠近中间状态的值即可。注意,如果负载的个数大小不定的话,要按照最坏的情况计算,上限值要按负载最多的时候计算,下限值要按负载最少的计算。

另一种选择方式是基于功耗的考虑。根据电路实际应用时,输出信号状态的频率或时间比选择。若信号Vout长期处于低电平,宜选择下拉电阻;若长期处于高电平,宜选择上拉电阻。为的是静态电流小。

"设计永远是妥协与权衡的艺术",至于最终选择那种方案,设计师的技术决策还是很重要的。电路设计的魅力也就在于此。

- 电源方案选择:隔离还是非隔离好?(06-02)

- 12位串行A/D转换器MAX187的应用(10-06)

- AGC中频放大器设计(下)(10-07)

- 低功耗、3V工作电压、精度0.05% 的A/D变换器(10-09)

- PIC16C5X单片机睡眠状态的键唤醒方法(11-16)

- 用简化方法对高可用性系统中的电源进行数字化管理(10-02)