揭秘高性能多路复用数据采集系统

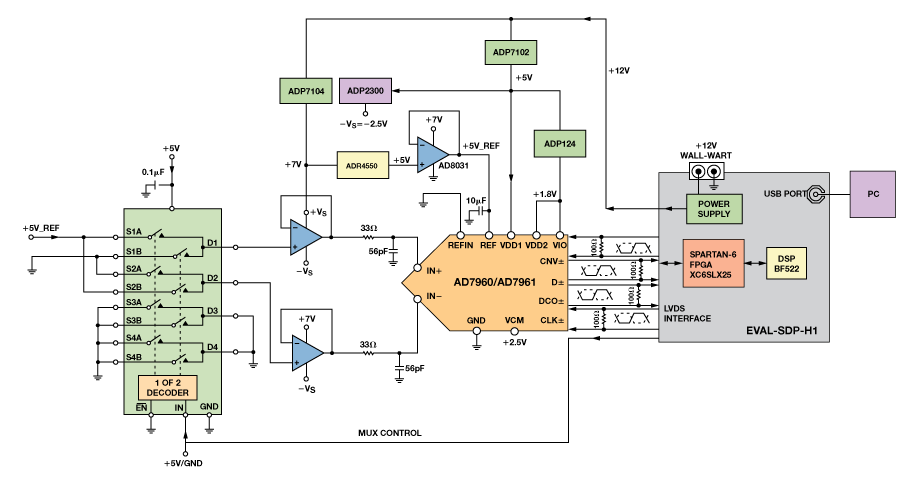

通道之一。 若要评估此系统,可连续开关ADG774的正负差分输入,以产生满量程阶跃。 两个超低失真运算放大器ADA4899-1缓冲多路复用器输出,并驱动18位、5 MSPS PulSAR® ADC AD7960。 RC滤波器(33 Ω/56 pF)有助于减少来自AD7960容性DAC输入端的反冲,并限制进入AD7960输入端的噪声。

图4. 多路复用数据采集系统简化信号链

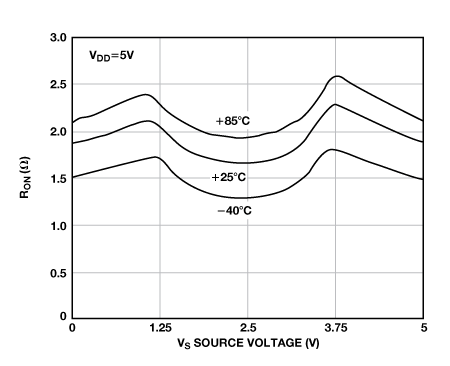

四通道2:1 CMOS多路复用器ADG774具有快速开关速度(tON = 7 ns, tOFF = 4 ns)、低导通电阻(RON = 2.2 Ω), 、宽带宽(f–3dB = 240 MHz)以及低功耗(5 nW),是便携式和电池供电型仪器仪表的理想之选。 ADG774的输入端连接5 V固定基准电压源和地,从而输出应从正满量程摆动到负满量程。 图5显示典型的导通电阻与输入电压关系曲线,该曲线输入电压范围为完整的0 V至5 V模拟输入,温度范围为–40°C至+85°C。 该性能水平可确保快速开关信号时拥有出色的线性度和低失真性能。

图5. ADG774导通电阻与输入电压的关系

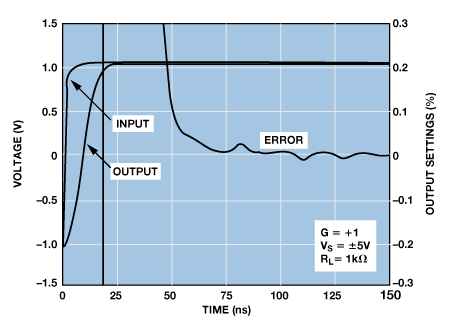

ADG774的输出连接至高输入阻抗放大器级。 ADA4899-1高速运算放大器具有超低噪声(1 nV/√Hz)和超低失真(−117 dBc)、600 MHz带宽以及310 V/μs压摆率性能。 该器件采用+7 V和−2.5 V电源供电,具有足够的裕量实现低系统噪声和失真。 如图6所示,在2 V p-p输入信号时,放大器的0.1%建立时间为50 ns,是驱动AD7960的理想之选。

图6. ADA4899-1典型建立时间

精密差分ADC AD7960具有同类一流的噪声和线性度性能,无延迟或流水线延迟,提供高精度(18位分辨率、±0.8 LSB INL、99 dB SNR和–117 dB THD)、快速采样(5 MSPS)、低功耗和低成本特性。 该器件采用+5 V (VDD1)和+1.8 V(VDD2和VIO)电源供电,以回波时钟模式转换时的功耗仅为46.5 mW (5 MSPS)。 其内核功耗随吞吐速率线性变化,因此非常适合低功耗、高通道密度应用。 可以利用低噪声LDO(比如源。ADP7104和ADP124)产生5 V和1.8 V电源。

该ADC的满量程差分输入范围通过外部基准电压源设为5 V或4.096 V。 若要充分利用动态范围,则输入信号必须从0摆动到VREF。 在该信号链中,5 V基准电压由高精度(±0.02%最大初始误差)、低功耗(950 µA最大工作电流)基准电压源ADR4550提供,该基准电压源具有出色的温度稳定性和低输出噪声。 轨到轨运算放大器AD8031缓冲外部基准电压。 该器件具有大容性负载稳定性,可驱动去耦电容,以便最大程度降低瞬态电流引起的尖峰。 AD8031适合从宽带宽电池供电系统到低功耗、高器件密度、高速系统的各种应用。

AD7960数字接口采用低压差分信号(LVDS),具有自时钟模式和回波时钟模式,提供ADC和数字主机之间高达 300 MHz(CLK±和D±)的高速数据传输。 LVDS接口允许多个器件共享时钟,从而降低数字线路的数量,并简化信号路由。 相比并行接口它具有更低的功耗,因此在多路复用应用中尤为有用。

AD7960在转换开始后大约115 ns内返回采集模式,采集信号的时间约为200 ns总周期时间的40%。 这一相对较长的采集时间减轻了放大器的带宽负担并降低了建立时间要求,使得差分输入更易于驱动。 5 MSPS吞吐速率允许多个通道以高扫描速率进行多路复用,因此高通道数系统所需的ADC数量更少。

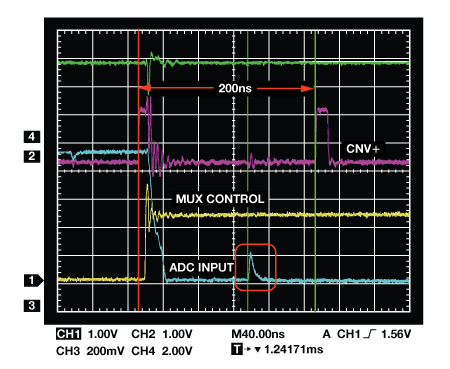

转换期间,AD7960的静态时间要求为90 ns至110 ns,期间多路复用器输入不可切换。 因此,为了避免破坏正在进行中的转换,必须在CNV±起始信号上升沿后不足90 ns或超过110 ns时切换外部多路复用器。 如果在此静态期间切换模拟输入,则最多可破坏15 LSB的当前转换。 应当尽可能早地切换模拟输入,从而有尽可能多的时间来摆动满量程信号并建立输入。

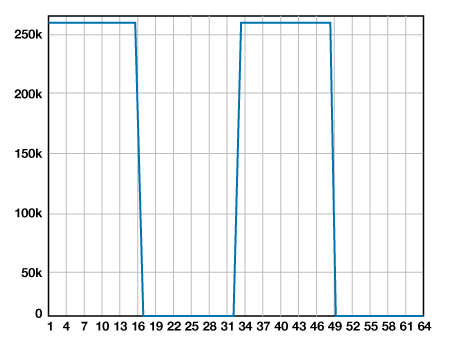

每16次转换之后,多路复用器将在CNV±上升沿过后,于–5 V和+5 V之间开关大约10 ns,如图7所示。这样会产生满量程差分阶跃,因此ADC输出从负满量程变为正满量程,如图8所示。

图7. 示波器曲线显示来自内部CAP DAC的反冲

图8. AD7960输出显示ADG774在每16次转换过后开关

这一开关时间延迟必须大于ADC的1.6 ns孔径延迟。 ADC输入端测得的信号显示来自AD7960中容性DAC的反冲约为1 V p-p(图7,红色高亮部分)。 为了确保输出完全建立,工作速率为5 MSPS时,驱动放大器必须在下一次转换开始前建立此瞬态,即大约80 ns采样时间内。 以较低的吞吐速率运行ADC可让该反冲有更多的采集时间去建立,从而多路复用器输入通道之间的串扰误差更低,同时满

- 8位高速A/D转换器TLC5510的应用(02-16)

- 毫欧姆电阻在汽车电子系统中的应用(05-11)

- 24位高精度模数转换器ADSl258的原理应用(11-28)

- 电子式互感器中数据采集系统误差补偿的设计与实现(01-01)

- 用于大型地震勘探网的高精度低功耗自检测数据采集系统(02-20)

- 为应变计应用选择合适的放大器(03-25)