逐次逼近型ADC:确保首次转换有效

立精度指定为 0.1%或 0.01%。指定的建立时间可能与 16 位精度的建立时间显著不同,因此选择驱动器之前应进行验证。

要特别注意多路复用应用中的建立时间。在多路复用器切换之后,要确保留出足够的时间,以便模拟输入能在转换开始之前建立至指定的精度。在配合 AD7606 使用多路复用器时,应为±10-V输入范围留出至少 80 µs的时间,为±5-V范围留出至少 88 µs,以便给选定通道足够的时间来建立至 16 位分辨率。面向精密SAR模数转换器的前端放大器和RC滤波器设计作者:Alan Walsh(模拟对话 话第 46 卷第 4 期,2012 年)为放大器的选择提供了更多细节。

模拟输入范围

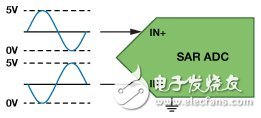

确保模拟输入处于指定的输入范围之内,要特别注意指定共模电压的差分输入范围,如图 5 所示。

图 5 共模电压下的全差分输入

例如,AD7960 18位、 5 MSPS SAR ADC的差分输入范围为–VREF 至 +VREF, 但折合到地的 VIN+ 和 VIN− −都应该处于–0.1 V至 VREF + 0.1 V的范围内,且共模电压应为 VREF/2左右,如表1所示。

表 1 AD7960的模拟输入规格

使 SAR ADC退出关断或待机模式

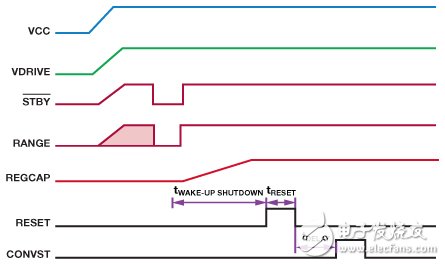

为了节能,有些SAR ADC会在空闲时进入关断或待机模式。在首次转换开始前,要确保ADC退出该低功耗模式。例如, AD7606 系列即提供了两种节能模式:完全关断和待机。这些模式由GPIO引脚STBY 和RANGE进行控制。

根据图6所示,当STBY 和RANGE返回高电平时,AD7606从完全关断进入正常工作模式,并配置为±10-V的范围。此时, REGCAPA、REGCAPB和REGCAP引脚上电至数据手册所述的正确电压。在进入待机模式时,上电时间约为 100 μs,但在外部基准电压源模式下,这需要大约13 ms。从关断模式上电时,经过所需的上电时间后,必须施加RESET信号。数据手册将上电与RESET上升沿之间所需时间规定为 tWAKE-UP SHUTDOWN。

图 6 AD7606 初始化时序

带延迟的 SAR ADC

人们普遍认为,SAR ADC 没有延迟,但有些 SAR ADC 确实存在延迟以便更新配置,因此,在经过延迟时间(可能为数个转换周期)之前,第一个有效转换代码可能未定义。

例如,AD7985 拥有两种转换工作模式:turbo和正常。Turbo模式(支持最快的转换速率,最高可达2.5 MSPS)不会在转换间关断。turbo模式下的第一次转换含有无意义的数据,应该予以忽略。另一方面,在正常模式下,第一次转换是有意义的。

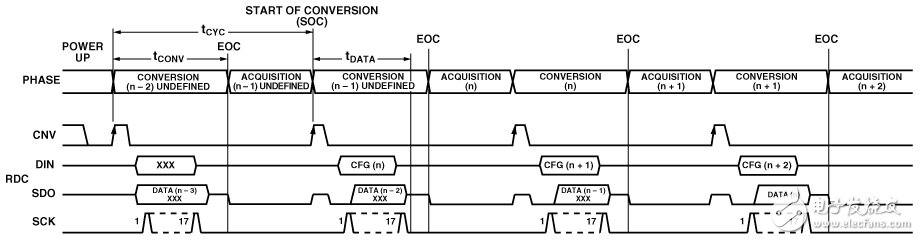

对于 AD7682/AD7689,上电后的前三个转换结果未定义,因为在第二个EOC之前,不会出现有效的配置。因此,需要两次伪转换,如图 7 所示。

图 7 AD7682/AD7689 的通用时序

当在硬件模式下使用 AD765x-1 时,在 BUSY 信号下降沿对 RANGE 引脚的逻辑状态进行采样,以决定下一次同步转换的模拟输入范围。在有效的 RESET 脉冲之后,AD765x-1 将默认在±4 × VREF 范围内工作,无延迟问题。然而,如果 AD765x-1 工作于±2 × VREF 范围内,则必须利用伪转换周期在 BUSY的第一个下降沿选择范围。

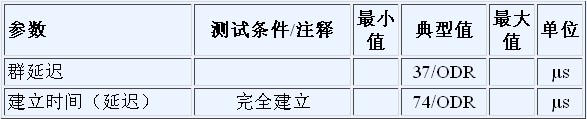

另外,有些SAR ADC(如AD7766/AD7767过采样SAR ADC)有后数字滤波器,结果会导致更多延迟。当将模拟输入多路复用至这类ADC时,主机必须等到数字滤波器完全建立后才能获得有效转换结果;经过该建立时间后,方可切换通道。

如表 2 所示,AD7766/AD7767 的延迟为 74 除以输出数据速率 (74/ODR)的商值。在运行于最高输出数据速率 128 kHz 时, AD7766/AD7767 支持 1.729 kHz 的多路复用器开关速率。

表 2 AD7766/AD7767的数字滤波器延迟

数字接口时序

最后,但同样重要的是,主机可以通过一些常见的接口选项(如并行、并行 BYTE、IIC、SPI 和菊花链模式下的 SPI)来访问 SAR ADC 的转换结果。要得到有效的转换数据,必须确保遵循数据手册中的数字接口时序规格。

结论

为了获得 SAR ADC 的第一个有效转换代码,务必遵循本文讨论的建议。可能还需要其他具体配置支持;请查看目标 SAR ADC 数据手册或者应用笔记,了解关于第一个转换周期开始之前初始化的相关内容。

参考文献

Kester, Walt. Data Converter Support Circuits. Chapter 7, Data Conversion Handbook.

Kester, Walt. "Which ADC Architecture Is Right for Your Application?" Analog Dialogue, Volume 39, Number 2, 2005.

Walsh, Alan. "Front-End Amplifier and RC Filter Design for a Precision SAR Analog-to-Digital Converte

- 精密逐次逼近型ADC基准电压源设计(03-30)

- 一种用于高速ADC的采样保持电路的设计(04-19)

- 带辅助DAC的双路Σ-Δ转换器的原理及应用(09-01)

- 采用开关电源为高速模数转换器供电(10-11)

- 在PCB级采用时间交替超高速模数转换器(01-28)

- 14位125Msps模数转换器ADS5500及其应用 (03-06)