基于DM6446中的高清数字视频显示接口设计方案

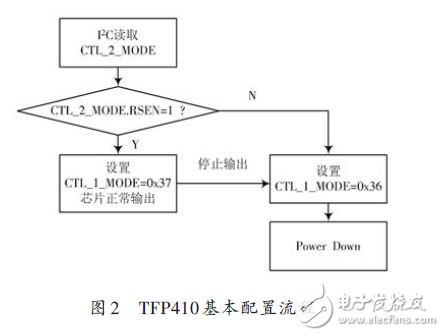

在图2 中,仅仅是列出了必须配置的寄存器,其余寄存器可以不用修改,一般不影响使用。配置CTL_1_MODE=0×37,使器件工作模式为:24 位数据宽度、单端像素时钟(VCLK)输入、在VCLK 上升沿采样输入数据。配置好TFP410后,DM6446只要按照高清数字视频的标准时序输出相应的图像数据和同步控制信息,就能够将OSD 上的内容通过DVI 接口显示到LCD 显示器上。

3 VENC及OSD配置

3.1 VENC配置

当VENC工作在标准模式(Standard Mode)下时,只能够输出标准的PAL/NTSC同步时序,在此模式下输出的画面分辨率最大只有720×576,这在许多场合已经不能满足使用需求。其实VENC 本身能够支持的画面分辨率远不止于此,只是若要输出大分辨率的画面,就必须自己编程产生视频同步控制时序,也即让VENC工作于非标准模式(Non- standard Mode)[6-8]。

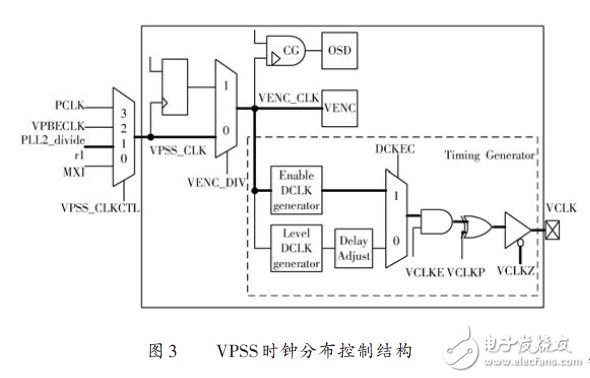

VENC主要由3大块组成:模拟视频编码模块(数模转换DACs)、数字视频输出模块(数字LCD 控制器)以及时序发生器(Timing Generator)。其中,模拟视频编码模块只能工作于标准模式下,因此,在配置输出非标准模式下的数字画面时,应该禁用DAC.对于数字LCD 控制器部分的编程,主要是设置输出图像数据的格式(并行24 位RGB888)以及配置输出LCD_OE(数据输出使能)指示信号。而对时序发生器的编程配置,则是输出高分辨率数字画面的关键所在,整个VPSS的时钟分布控制结构如图3所示。

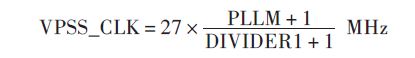

根据VESA DMT标准,显示1 080P画面所需像素时钟为148.5 MHz.从图3 可以看到,VPSS 的时钟共有4个来源可以选择:其中MXI为芯片主要输入时钟,其频率仅有24 MHz,不能满足要求;PCLK是由外部输入的视频采集时钟,在这里也不适用;VPBECLK是专门的辅助时钟输入,而PLL2_divider1是内部倍频时钟,这两者经过配置都可以在高清数字视频显示接口设计中使用。在这里,主要是采用PLL2_divider1时钟。

通过配置锁相环PLL2 控制器的PLLM=21,divID-ER1=3,便可以得到148.5 MHz的像素时钟。通过寄存器VPBE_PCR.VENC_div 位可以选择VENC_CLK 是否为VPSS_CLK 的一半,当VENC_div=1( 需要VPSS_CLKCTL.DACCLKEN=1)时,输入时钟将被2 分频,VENC_CLK 变成74.25 MHz,这正好是显示720P 画面所需的像素时钟。而且,148.5 MHz的像素时钟也能够同时支持WUXGA 画面的显示。相同的时钟输入能够同时满足多种高清分辨率图像的显示要求,这就为不同显示分辨率间的切换提供了编程上的便利性。

输出给TFP410 的像素时钟VCLK,以VENC_CLK为基准,可以通过时钟样式寄存器VENC_DCLKPTNn以及VENC_DCLKPTNnA(n=0~3)自定义自己的输出波形和周期,可配置的波形周期为64位。从图3中可以看到,整条VCLK 输出链路还受内部使能位VCLKE、极性控制位VCLKP、以及输出管脚三态控制VCLKZ的层层控制。要输出时钟,则必须正确配置所有的控制位。在这里,通过配置,使得输出时钟VCLK 与内部VENC_CLK 相等,时钟的流向如图3 中的加粗黑实线所示。

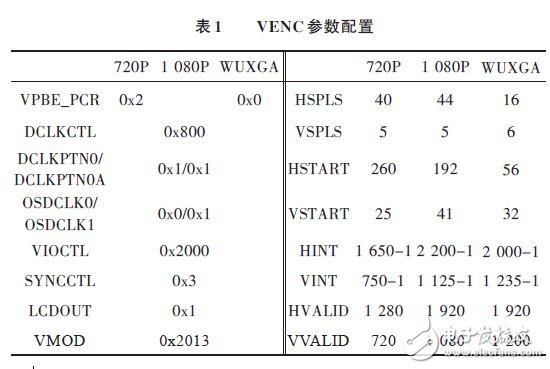

经过DCLK 的配置,已经能够得到显示720P,1 080P、WUXGA 画面所需的74.25 MHz 及148.5 MHz的像素时钟VCLK.VENC在VCLK 的上升沿输出图像数据,不过由于实际传输的数据有些是用于视频消隐的,必须有相关信号来指示有效视频数据的范围,这就是视频同步时序信号。视频同步主要有行同步(HSYNC)和场同步(VSYNC),具体定义可以参见相关文档[3]。最后,依据VESA DMT标准和实测结果,得到的整个VENC相关寄存器配置情况如表1所示。

表1主要给了在只提供148.5 MHz像素时钟情况下,要实现720P,1 080P和WUXGA 分辨率画面显示,VENC所必须配置的寄存器的值。按照表中的参数进行设置后,输出时钟VCLK、编码时钟VENC_CLK以及窗口时钟OSD_CLK三者相等。VPBE_PCR可用于配置时钟频率在74.25 MHz和148.5 MHz之间切换,以满足在720P和1 080P(或WUXGA)显示分辨率下系统对编码时钟的需求。

3.2 OSD配置

经过VENC的配置,系统已经支持高清数字视频的输出,由于VENC 编码数据来自于OSD 模块,所以要输出有效数据,还必须对OSD模块进行配置。DM6446的OSD 模块共支持两个视频窗口VIDWIN0/1和两个位图窗口OSDWIN0/1,还有透明矩形光标窗口(Regular Cur-sor)。其中,视频窗口VIDWIN0作为所有窗口的画布窗口,其他所有窗口的显示范围都必须在此窗口内,而且在显示其他窗口之前也必须使能 VIDWIN0.所有的OSD窗口都有独立的使能控制位,当所有的窗口都不使能时,VENC 将只显示OSD 中由寄存器MODE.BCLUT、MODE.CAB

- 12位串行A/D转换器MAX187的应用(10-06)

- AGC中频放大器设计(下)(10-07)

- 低功耗、3V工作电压、精度0.05% 的A/D变换器(10-09)

- PIC16C5X单片机睡眠状态的键唤醒方法(11-16)

- 用简化方法对高可用性系统中的电源进行数字化管理(10-02)

- 利用GM6801实现智能快速充电器设计(11-20)