可编程增益跨阻放大器的双通道色度计

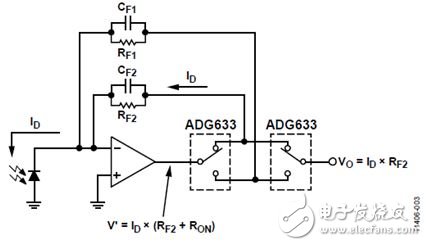

它表示增益误差。 但是,由于其中一个ADG633位于反馈环路之外,该级的输出阻抗即为ADG633的导通电阻(通常52 Ω),而非闭环工作时与运算放大器输出有关的极低输出阻抗。ADG633漏电流(典型值5 pA)引起的误差可忽略不计。

哪怕诸如ADA4528-1这类最好的轨到轨输出放大器,其输出都无法完全摆动至供电轨。 此外,ADA4528-1上的输入失调电压可以为负,虽然其数值非常小。 运算放大器ADA4805-1不是通过一个负电源来保证放大器绝不削波,并且保证它能驱动至0.0 V,而是提供一个100 mV缓冲电压来偏置光电二极管阳极和ADA4528-1。ADA4805-1非常适合用作基准电压缓冲器,因为当驱动去耦用大容性负载时,它能保持单位增益稳定性。 另外还使用第二个ADA4805-1来缓冲用以设置LED电流的数字电位计AD5201输出。

图3. 可编程增益跨阻放大器

光电二极管放大器输出电压可在0.1 V至5.0 V范围内摆动。对于33 kΩ范围而言,4.9 V输出范围对应148.5 μA的满量程光电二极管电流。 对于1 MΩ范围,其对应4.9 μA的满量程光电二极管电流。 使用1 MΩ的增益设置工作时,务必保护光电二极管不受外界光线影响,以防放大器饱和。 虽然下文所述的同步检波方案能够有力地衰减任何不与LED时钟同步的频率,但若ADC返回饱和数据,检波方案将无法正常工作。

各通道的增益设置可通过FPGA板独立选择。

ADC采样速率和调制频率选择

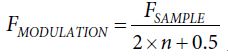

AD7175-2 ADC配置有sinc5+sinc1滤波器,输出数据速率为250 kSPS,可采样单周期建立对两个通道采样。这种配置使得各通道的有效采样速率为25 kSPS(各通道每隔40 μs输出数据)。 任何高于12.5 kHz的频率(例如方波调制的奇数谐波)都会混叠回到ADC通带中,只要其不是刚好位于调制频率之上,同步解调级就会抑制这些频率。 为了防止调制波形的混叠频率折回到基频,应根据以下关系选择调制频率:

其中:

FMODULATION为调制频率。

FSAMPLE为ADC有效输出数据速率。

n为整数(对应于调制频率的谐波)。

例如在本系统中,有效输出数据速率为25 kSPS,因此,如果需要1 kHz左右的调制频率,该频率必须是1020 Hz (n = 12)或943 Hz (n = 13)以避免混叠问题。 采样这种方法选择调制频率,前端即无需使用陡峭的抗混叠滤波器。

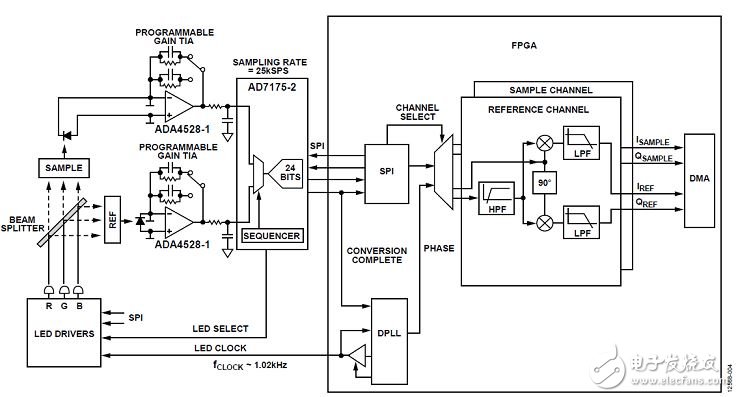

数字同步检波

本电路不是在硬件中实现同步检波,而是获得时间采样数据并利用FPGA实现数字同步检波。 图4是FPGA中实现的数字同步检波模块的示意图。 FPGA产生交流激励信号驱动LED,以数字方式产生的正弦波在数字锁相环中锁定该信号。 输入信号与数字正弦波和90°相移版本相乘,产生两个低频解调信号,其分别与输入信号在调制频率的同相和正交分量成正比。 如图4所示,幅度为这两个分量的平方和之根。 有关该解调技术的更多信息,请参阅"了解详情"部分。

图4. 包括FPGA同步检波器的系统框图

电源

EVAL-CN0363-PMDZ板由外部6 V至12 V直流电源供电。

电路的模拟部分由来自低压差稳压器ADP7102的AVDD = 5 V供电。 电路的数字部分由低压差稳压器ADP1720产生的IOVDD = 3.3 V供电。 或者,IOVDD也可以通过链路选项由PMOD连接器VCC提供。

2.5 V基准电压由AD7175-2 ADC的内部2.5 V基准源提供。

电路性能测量

为了验证系统的噪声性能,应在禁用所有LED的情况下获取数据。 同步检波器依然工作在LED时钟频率,但不会检测到任何与该时钟同步的光信号,因此,它会消除所有直流和交流信号。 表1所示为无噪声位性能。

表1. 无噪声位性能1

1 采样速率 = 25 kSPS,激励频率 = 1020 Hz,输出滤波器带宽 = 100 Hz。

常见变化

改变光电二极管放大器上反馈电阻的值即可改变放大器增益,这是一种自定义电路的简单方法,可用于不同光照水平的特定应用。 然而,补偿电容也必须改变,以保持带宽不变,并保证放大器的稳定性。

对于极低水平光照测量系统而言,同步检波器的输出低通滤波器的截止频率可设为低得多的频率值,以便具有最佳性能,但代价是测量周期较长。

由于LED的光输出随温度变化而改变,系统以样本和参考通道的比例进行测量。 光电二极管的增益容差最大值为±11%;因此,由于LED输出随时间和温度的变化而改变,比例的变动在一定程度上存在漂移。 增加光反馈网络来控制LED光输出可降低其随温度的变化,使精确的单端测量成为可能。

可以不使用方波来调制LED,而用FPGA中的DDS或PWM来产生正弦波调制。 正弦波调制可减少信号的谐波成分,使滤波更简单,并降低噪声。

电

- ADI:监测环境污染,AD7175-2可以做很多(12-31)

- 电源管理总线的结构与优势(11-19)

- 新型灌封式6A至12A DC-DC μModule稳压器系列(11-19)

- 低电压PLD/FPGA的供电设计(01-24)

- 基于FPGA的高精度数字电源(02-12)

- 功率分配系统(PDS)设计:利用旁路电容/去耦电容(04-29)