快速设置的GaAs pHEMT微波开关

开关速度是个涉及多个事件的复杂参数,每个事件都有自己的持续时间。借助已申请专利的pHEMT技术,M/A-COM Technology Solutions公司(下文简称为M/A-COM)已经找到了一种可缩短其中一个事件--开关的设置时间--的方法,从而给基于分组通信网络和雷达系统等须严格控制时域参数的系统带来了福音。在从10MHz到20GHz这一系列开关中都采用了该技术,其设置时间可短至20ns。

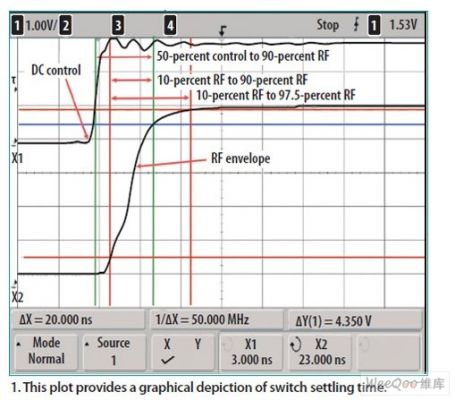

开关速度和设置时间(settling time),或者栅迟滞(gate lag),都被用来描述高速开关性能,但这两个参数有区别且往往被误解。开关速度是指当控制信号使开关从"截止"转为"导通"时,射频包络线从10%变化到90%所需的时间(图1)。从控制信号值达到其50%开始到RF包络线达到其90%的这段时间,传统上标记为ton。RF包络从10%变化到90%所需的上升时间标记为trise。当控制信号使开关从"导通"变为"截止"时,从控制信号值达到其50%开始到RF包络线从90%降至10%的这段时间是 toff。而RF包络线从90%降至10%的这段单独的时间是tfall。栅迟滞定义了开关经过RF包络线的90%后,或者10%后的设置时间特性。

图1:开关设置时间的图示说明。

不幸的是,开关过渡时间的最后10%可造成对传统开关速度规范的误解,因为最后的10%与先前90%的变化速率不同。历史上看,响应呈对数形态,而最后10%所花时间接近整个设置时间。通常情况,对于达到90%这一点需10ns的开关来说,达到100%这一点可能需要数百ms。这个长的设置时间(栅迟滞),会给许多系统带来问题。

根据现有的设备和方法,可通过测量器件的功率从90%变到以后设置起的某个值,如97.5%或100%,所需的时间来计算器件的栅延迟。此外,还可通过在控制信号改变后,观察两个固定时间点的阻抗变化来测量,因为开关器件在"开"状态呈低阻态,在"关"状态呈高阻态。例如,器件的栅迟滞可被描述为:在控制信号改变后10μs到10ms这段时间阻抗发生了0.5Ω的变化。虽然无法消除栅迟滞,但M/A-COM Technology Solutions已开发出针对栅迟滞导致的延迟的解决方案。

无论是看作延迟或开关阻抗变化,在许多测试应用及其它系统中,开关都必不可少。一些复杂的基于分组的调制方案,依靠快速发送/接收或分集开关来优化数据吞吐量、降低信噪比。如果当第一个数据包已通过它传输时,开关仍处在设置时期,则包络形状可能是圆的,从而有可能损害数据。对于高数据速率通信应用,快速的设置性能可以显著缩短发射前的等待时间。可用数据传输时间多,则相当于提高了吞吐量。

设置时间短的开关还可带来热管理方面的好处。当射频功率施加到尚未完全设置起来的器件上时,在器件达到稳定状态前,功耗会显着增加。更快的设置速度意味着降低了由于设置之前的串联电阻引入的功耗,另外还可在高功率下实现更低的工作结温。

开关延迟主要与改变存储在有源器件、相关电路内静态电荷、与时间相关的充/放电衰减效应有关。有几个因素造成的迟滞现象,可通过阻抗和容抗对其描述。场效应管(FET)的栅极体积小,且存在一定损耗,为对直流和射频进行隔离,大多开关设计中通常采用大阻值的栅电阻。栅电阻成为决定阻容(RC)时间常数的一个因素。对于任何状态的改变(作为一阶近似),必须耗尽或恢复器件沟道、且必须创建或清除栅周围的电场。

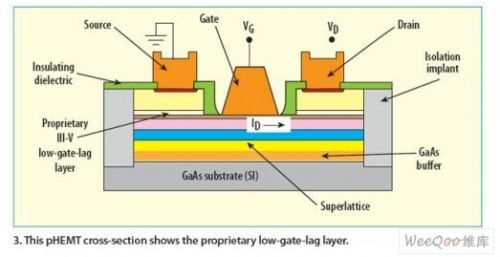

在器件级,参考砷化镓MESFET/pHEMT的简化截面,可以理解开关速度和任何相关的栅迟滞(图2)。射频开关时间由沟道区的电荷主导,电荷位于栅附近的栅控和非栅控凹陷区。器件的导通时间是当施加控制信号后,将电荷通过沟道从源极转移到漏极所需的时间。导通时间是用电荷填充沟道区所需相应延迟时间的函数。电荷包括与栅极容抗相关的沟道电荷,以及非栅控凹陷区内的表面陷阱电荷。关断时间定义则相反,只有彻底移除沟道和凹陷区内的电荷,器件才会完全截止。

通过器件截面图还能直观地认识相对快的trise(即RF包络线从10%上升到90%所需的时间)、RF包络从90%下降到10%所需的时间 tfall、以及RF包络从90%过渡到100%所需的相对很长的栅迟滞时间。与直接位于栅下方的耗尽区相关的沟道电荷,占这部分电荷的主要部分。通过对栅极终端施以正确的极偏置,可相对快地将电荷移进和移出栅极区。另一方面,非栅控凹陷区内的电荷以表面状态和界面陷阱等形态被集聚起来,它们对施加的偏压相对不敏感,只能通过由肖特基二极管形成的阻容(RC)电路充放电。这些表面电荷的填充和移出是一个缓慢过程,直接导致栅迟滞开关时间延长。

图3: 具有专利的低栅迟滞层的pHEMT剖面图。

为解决由栅迟滞主导的状态变化所引致的射频开关时间