∑-ΔADC(第二部分):调节器

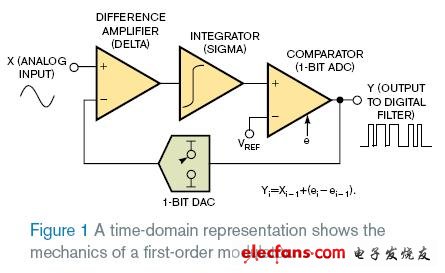

Σ-Δ转换器使用从调节器得到的许多采样值产生1bit码流。Σ-ΔADC以高采样速率使用输入信号量化器完成这个任务。像所有的量化器一样,Σ-ΔADC调节器获取输入,产生数字码流表征输入电压。可以观察时域或频域的Σ-Δ调节器。如果看时域表现,可以见一阶调节器的结构(图1)。

调节器测量模拟输入信号和反馈DAC的模拟输出。随后一个积分器测量求和节点的模拟电压输出,为1位ADC呈现出一个斜坡信号。1位ADC转换积分器输出信号为数字一或零。使用系统时钟,ADC将1位数字信号送到调节器输出,也通过反馈回输入,在这里1位DAC为等待。

1位ADC将信号量化为离散的输出编码,带有转换器的量化噪声(ei)。调节器输出等于输入信号加上量化噪声(ei–ei–1)。如这个公式所示,量化噪声为调节器当前误差(ei)减去前一个误差(ei–1)的微分。时域输出信号为以采样频率FS的输入信号脉冲波形。如果将输出脉冲序列平均,它等于输入的信号值。

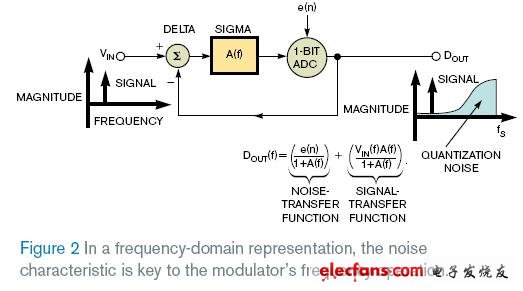

频域图反映了不同的问题(图2)。时域输出脉冲在频域内表现为输入信号(或毛刺)和变形的噪声。图2的噪声特性是调节器频率作用的关键。

不像大多数量化器,Σ-Δ调节器包括形成量化噪声的积分器。调节器输出的噪声频谱并不平滑。更重要的,在频率分析中,可以看到积分器怎样在更高频率处形成噪声,便于产生更高分辨率的结果。

图2中调节器输出显示了调节器的量化噪声在0Hz时开始为低电平,快速上升,然后在调节器采样频率为最大值处稳定。

二阶调节器进行两次积分,而不是仅有一次,是最小化低频率量化噪声的一种好方法。大多数Σ-Δ调节器具有更高的阶数。例如,更常用的Σ-Δ转换器的设计包括二、三、四、五或六阶调节器。多阶调节器在更高频率形成更大的量化噪声。

- ∑-ΔADC(第三部分):新诀窍(02-19)

- ∑-ΔADC(第一部分):基本拓扑(02-15)

- ∑-ΔADC应用笔记(02-16)

- 350-W、双相交错式预调节器设计评价(08-01)

- 驱动中型LED背光系统的集成方案(10-03)

- 提高电源转换效率的交错式PFC控制技术及应用(04-06)