英特尔10纳米可实现多达25%的性能提升

智能互联时代,数据洪流汹涌而生,对计算力的需求前所未有。英特尔始终以领先的制程工艺提供不断跃升的计算力,并将晶体管密度作为引领制程工艺发展的首要准则。英特尔以突破性技术和持续创新不断打破摩尔定律失效"魔咒",过去15年里在业界广泛应用的主要制程工艺创新都由英特尔推动,并始终拥有至少三年的领先优势。

晶体管密度:

衡量制程工艺领先性的首要准则

目前一些竞争友商公司的制程节点名称并不准确,无法正确体现这个制程位于摩尔定律曲线的哪个位置。摩尔定律是指每一代制程工艺的晶体管密度加倍,纵观发展史,业界在命名新制程节点时会比上一代缩小30%,这种线性缩放意味着晶体管密度提高一倍,是符合摩尔定律的。近来,也许是因为进一步的制程升级越来越难,一些竞争友商公司背离了摩尔定律的法则,即使晶体管密度增加很少,或者根本没有增加,但他们仍继续推进采用新一代制程节点命名。

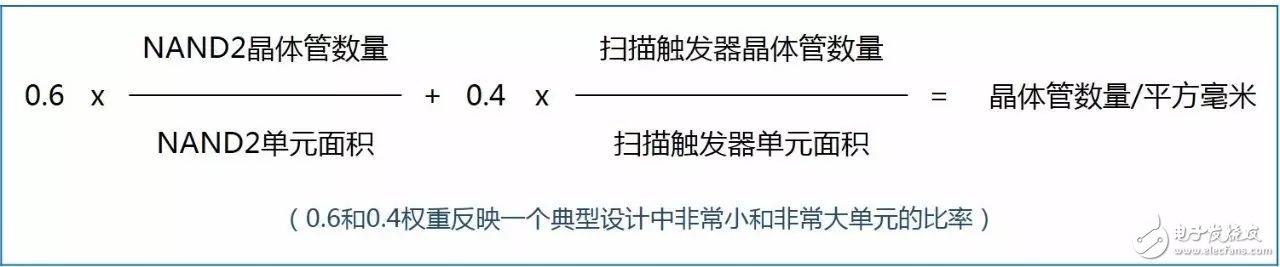

晶体管密度是衡量制程工艺领先性的首要准则。英特尔提出的指标是基于标准单元的晶体管密度,包含决定典型设计的权重因素,从而得出一个之前被广泛接受的晶体管密度公式:

这个公式可用于任何制造商的任何芯片晶片,且已被业界广泛使用,它能够明确、一致地测量晶体管密度,并为芯片设计者和客户提供关键信息,准确比较不同制造商的制程。通过采用这个指标,业界可以改变制程节点命名的乱象。

英特尔10纳米:

晶体管密度是其他竞争友商"10纳米"的2倍

英特尔10纳米制程采用第三代FinFET技术,相比其他竞争友商"10 纳米"制程领先整整一代。英特尔10纳米制程的晶体管密度达到每平方毫米1.008 亿个晶体管,是之前英特尔14纳米制程的2.7倍,是业界其他竞争友商"10纳米"制程的约2倍。

相比之前的14纳米制程,英特尔10纳米制程实现多达25%的性能提升和45%的功耗降低。全新增强版的10纳米制程——10++,可将性能再提升15%并将功耗再降低 30%。

英特尔10纳米制程计划于2017年底投产,2018年上半年实现量产。

英特尔14纳米:

晶体管密度与其他竞争友商"10纳米"相当

相比于业界其他竞争友商的16/14纳米制程,英特尔14纳米制程的晶体管密度是他们的约1.3倍。业界其他竞争友商"10 纳米"制程的晶体管密度与英特尔14纳米制程相当,却晚于英特尔14纳米制程三年。

英特尔14纳米制程采用第二代 FinFET 技术,正处于量产阶段。英特尔14纳米制程的持续优化使其性能比最初的14纳米制程可以提升多达 26%,也可以在相同性能下降低50%以上的有效功耗。英特尔14+制程的性能比最初的14纳米制程提升了12%,而英特尔14++制程在此基础上又将性能提升了24%,超过业界最佳的其他14/16纳米制程20%。

超微缩技术:

提供超乎常规的晶体管密度

超微缩是英特尔用来描述从14纳米到10纳米制程,晶体管密度提高2.7倍的术语。超微缩为英特尔14纳米和10纳米制程提供了超乎常规的晶体管密度,并延长了制程工艺的生命周期。尽管制程节点间的开发时间超过两年,但超微缩使其完全符合摩尔定律。

22FFL

物联网和移动产品创新利器

22FFL是世界上第一个专门面向低功耗物联网和移动产品的FinFET技术,它基于英特尔近年22纳米/14纳米制程的生产经验,带来性能、功耗、密度和易于设计等优势,特别是将为中国带来巨大的创新机遇。

与先前的22GP(通用)制程相比,全新22FFL制程的漏电量最多可减少100倍。22FFL制程工艺可提供与14纳米制程晶体管相媲美的驱动电流,同时实现比业界28纳米制程更高的面积微缩。

前沿技术研发:制胜未来

英特尔拥有完整的前沿研发计划,一些正处于研究中的前瞻项目包括:纳米线晶体管(Nanowire Transistor)、III-V材料( III-V Materials)、3D堆叠(3D Stacking)、高密度内存(Dense Memory)、微缩互联(Scaling Interconnects)、极紫外(EUV)光刻技术(Extreme Ultraviolet Lithography)、自旋电子(Spintronics)、神经元计算(Neuromorphic Computing)等。

- 大数据解决方案,布局智能安防(07-04)

- 基于英特尔技术的几大汽车创新设计(06-15)

- 四大案例让你了解最先进的物联网网关解决方案(04-08)

- 物联网网关四大案例解决方案(11-21)

- 物联网应用实例(02-23)

- 相比VR/AR 英特尔的MR不过时?(07-18)