lpc54102引脚图_lpc54102引脚说明

lpc54102简介

LPC54102 MCU是基于 ARM Cortex-M4 的嵌入式应用微控制器。这些器件包括可选 ARM Cortex-M0+ 协处理器、104 KB 片上 SRAM、高达 512 KB 的片上 flash、五个通用定时器、一个带 PWM 功能的状态可配置定时器 (SCTImer/PWM)、一个 RTC/ 警报定时器、一个 24 位多速率定时器 (MRT)、一个重复中断定时器 (RIT)、一个窗口化看门狗定时器 (WWDT)、四个 USART、两个 SPI、三个带高速从机模式的超快速模式 I 2C 总线接口和一个 12 位 5.0 MSPS ADC。

ARM Cortex-M4 是一款 32 位内核,具有低功耗、易调试、支持模块高度集成等多种系统增强优势。 ARM Cortex-M4 内核 CPU 采用 3 级流水线和哈佛架构,具有独立的本地指令和数据总线以及用于系统外设的第三总线,同时还包含一个支持不确定分支操作的内部预取单元。ARM Cortex-M4 支持单周期数字信号处理器和 SIMD 指令。内核中集成硬件浮点运算单元。

ARM Cortex-M0+ 协处理器是一款高能效、简单易用的 32 位内核,该产品与 Cortex-M4 内核的代码和工具相互兼容。Cortex-M0+ 协处理器可提供高达 100 MHz 的性能,具有简单指令集和缩减的代码大小。在 LPC5410x 中,Cortex-M0 协处理器硬件乘法是作为 32 周期的迭代乘法器来实现的。

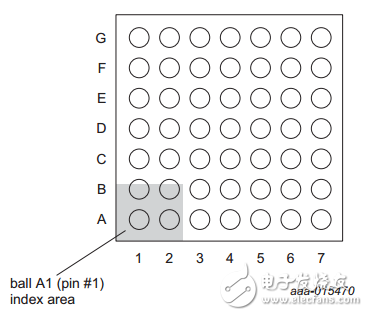

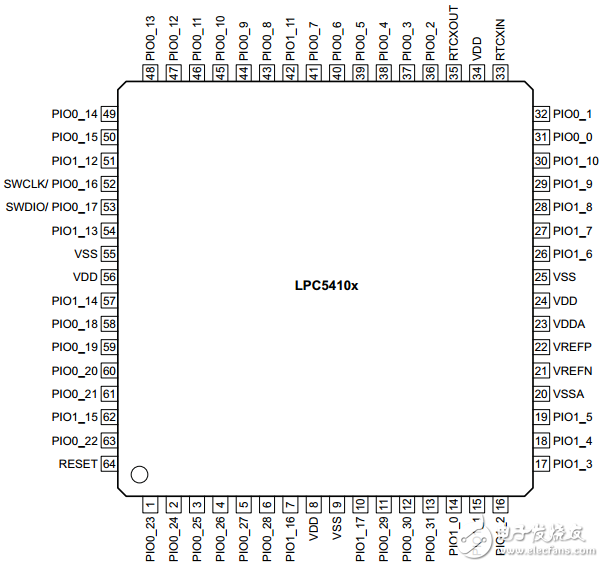

lpc54102引脚配置

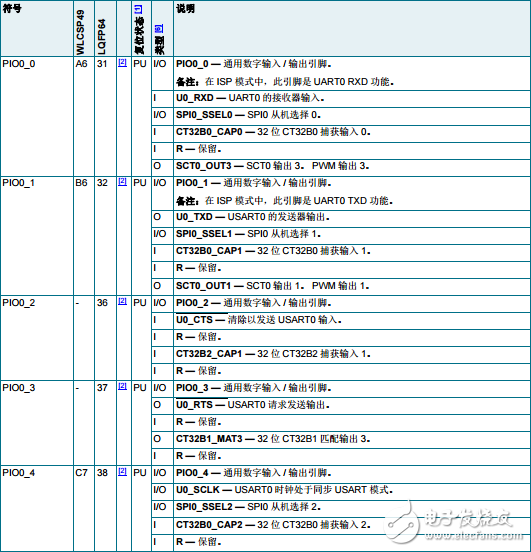

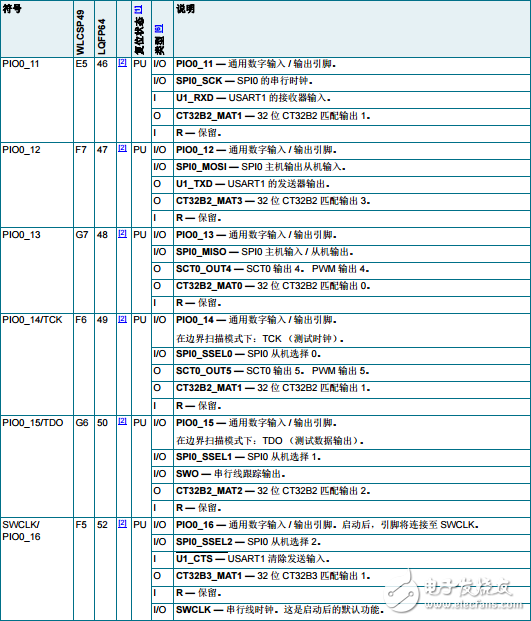

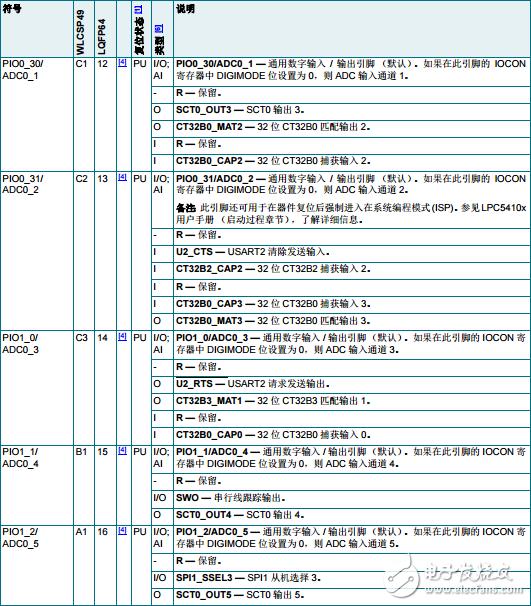

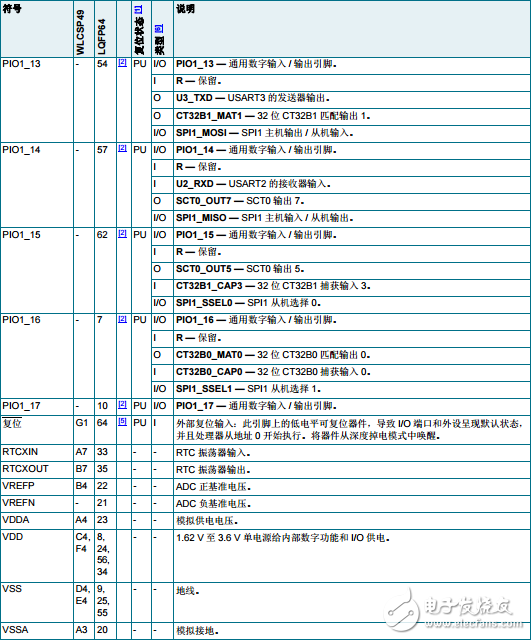

lpc54102引脚说明

在LPC54102 上,数字引脚可分组至两个端口。每个数字引脚可能会支持最多四个不同的数字功能、一个模拟功能,包括通用 I/O (GPIO)。

[1] PU = 输入模式,已使能上拉电阻 (上拉电阻将引脚拉高至 VDD)。 Z = 高阻抗,禁用上拉或下拉电阻。复位状态反映引脚在复位时无启动代码操作的状态。不同电源模式下的引脚状态请参见 6.2.2 章 " 不同电源模式下的引脚状态 "。有关未使用引脚的端接请参见 6.2.1 章 " 未使用引脚的端接 "。

[2] 具有可编程干扰滤波器的 5 V 兼容焊盘 (VDD 存在时,容限为 5 V ; VDD 不存在时,容限不超过 3.6 V);提供具有 TTL 电平和迟滞的数字 I/O 功能;标准驱动强度。请参见图 27。输入滤波器抑制的峰值或干扰脉冲宽度为 3 ns 至 16 ns (仿真值)。

[3] 真开漏引脚。I2C 总线引脚符合 I2C 总线规范,支持 I2C 标准模式、I2C 快速模式和 I2C 超快速模式。此引脚要求进行外部上拉,以提供输出功能。电源关闭时,此引脚处于悬空状态,不会干扰 I2C 线路。开漏配置适用于此引脚上的所有功能。

[4] 5 V 兼容引脚提供带有可配置模式、可配置迟滞和模拟输入的标准数字 I/O 功能。配置为模拟输入时,引脚的数字部分禁用,且引脚并非 5 V 兼容。

[5] 复位焊盘。带干扰滤波器和迟滞功能的 5 V 兼容焊盘。输入滤波器抑制的尖峰或干扰脉冲宽度为 3 ns 至 20 ns (仿真值)。

[6] I = 输入; AI = 模拟输入; O = 输出。

lpc54102 相关文章:

- lpc54102例程(两种方案代码详解)(07-25)

- lpc54102的特性(09-20)

- LT3751如何使高压电容器充电变得简单(08-12)

- 三路输出LED驱动器可驱动共阳极LED串(08-17)

- 浪涌抑制器IC简化了危险环境中电子设备的本质安全势垒设计(08-19)

- 严酷的汽车环境要求高性能电源转换(08-17)