stm32f103zet6引脚图及引脚定义

stm32f103zet6是一种嵌入式-微控制器的集成电路(IC),是由ST公司开发的STM32F1系列的其中一种,芯体尺寸是32位,速度是72MHz,程序存储器容量是256KB,程序存储器类型是FLASH,RAM容量是48K。

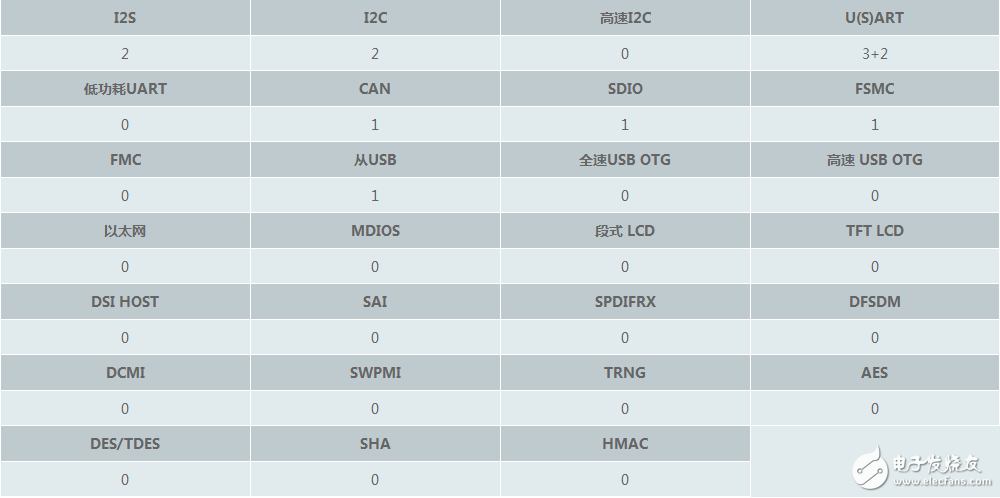

stm32f103zet6详细参数如下:

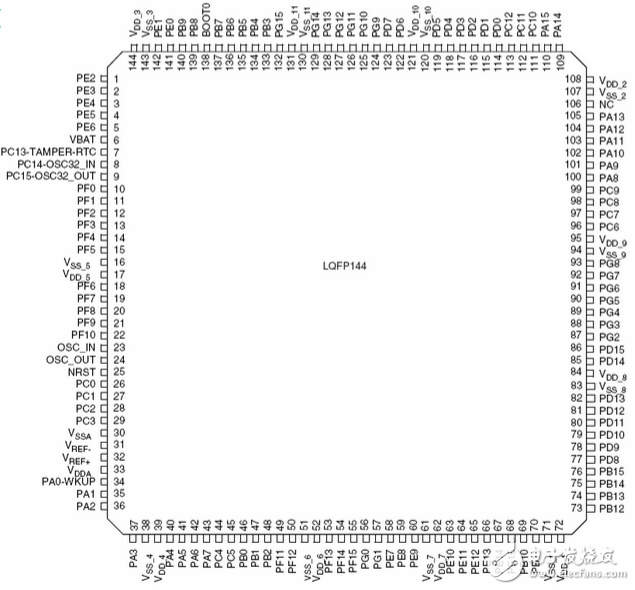

stm32f103zet6引脚图如下:

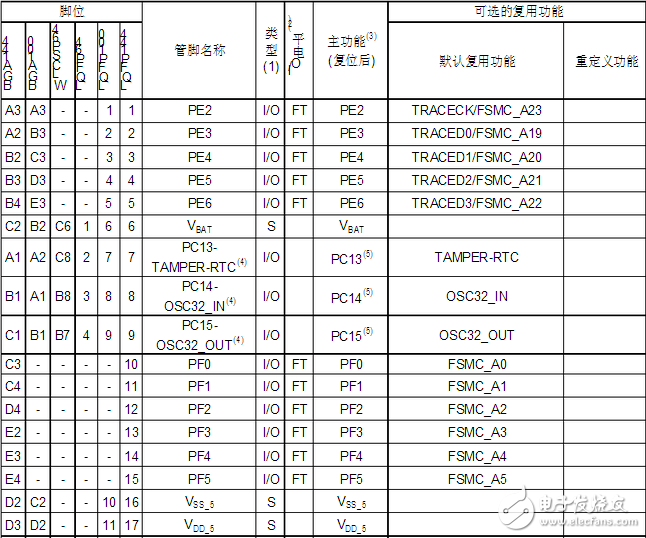

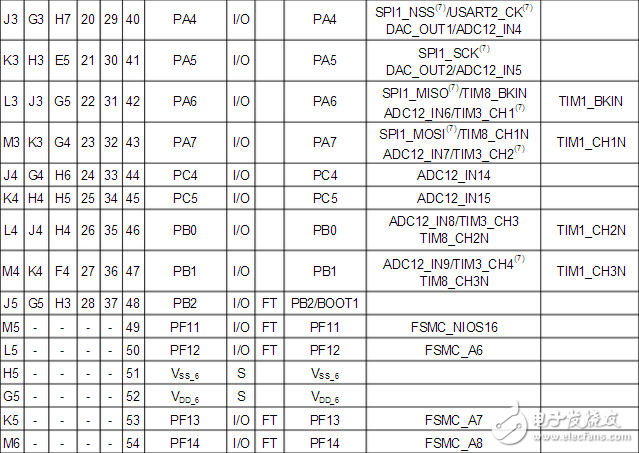

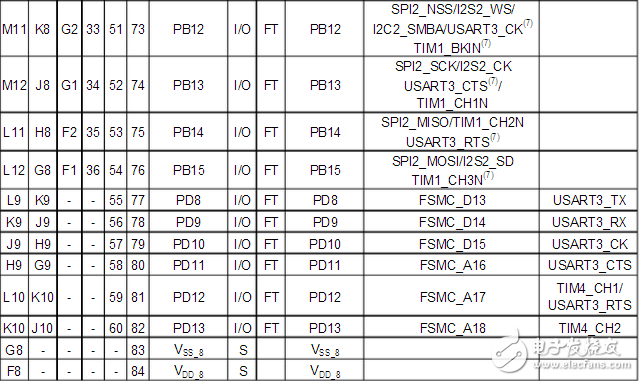

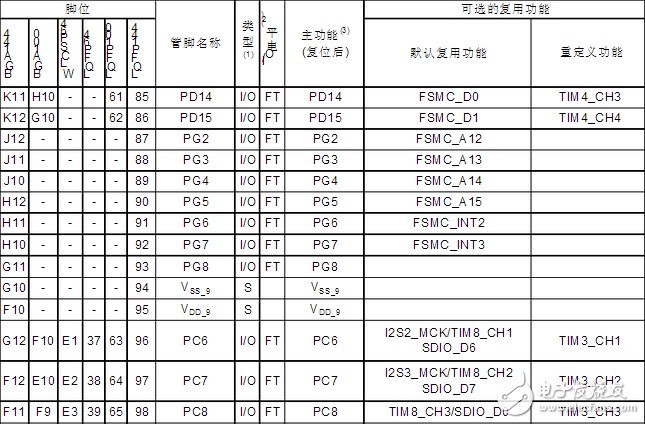

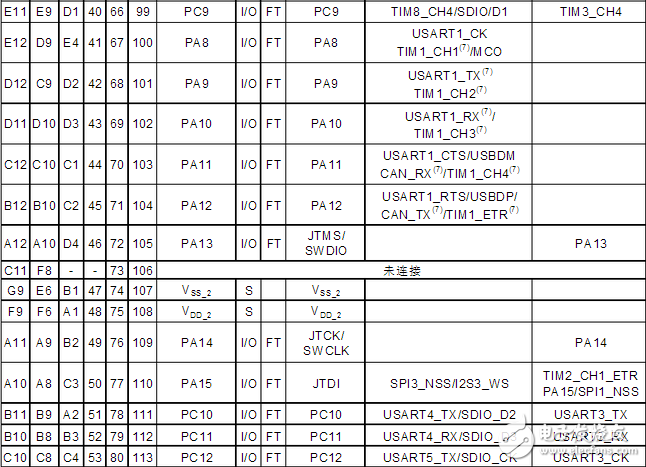

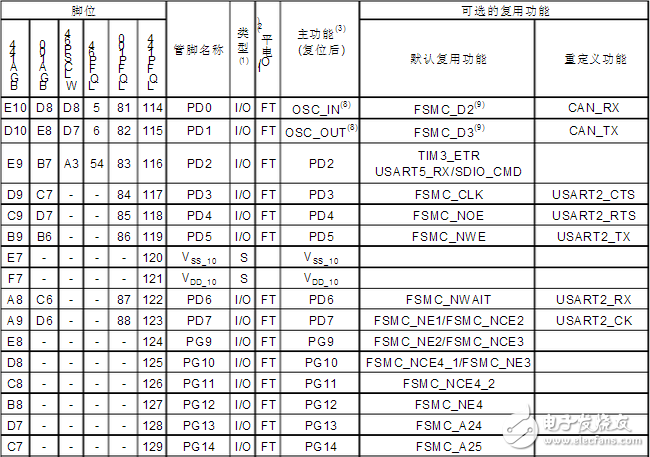

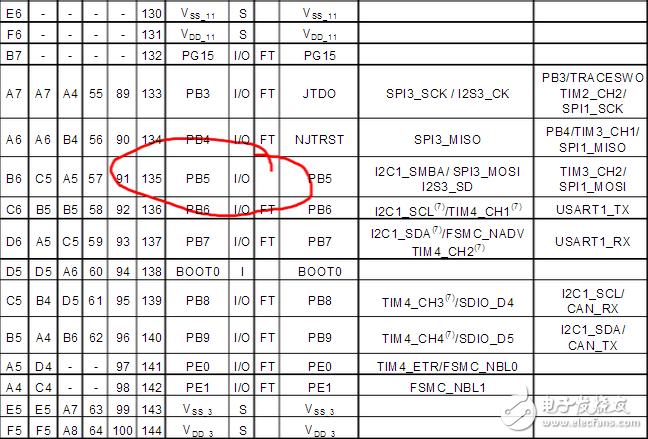

stm32f103zet6引脚定义如下:

1. I = 输入,O = 输出,S = 电源, HiZ = 高阻

2. FT:容忍5V

3. 有些功能仅在部分型号芯片中支持。

4. PC13,PC14和PC15引脚通过电源开关进行供电,而这个电源开关只能够吸收有限的电流(3mA)。因此这三个引脚作为输出引脚时有以下限制:在同一时间只有一个引脚能作为输出,作为输出脚时只能工作在2MHz模式下,最大驱动负载为30pF,并且不能作为电流源(如驱动LED)。

5. 这些引脚在备份区域第一次上电时处于主功能状态下,之后即使复位,这些引脚的状态由备份区域寄存器控制(这些寄存器不会被主复位系统所复位)。 关于如何控制这些IO口的具体信息,请参考STM32F10xxx参考手册的电池备份区域和BKP寄存器的相关章节。

6. 与LQFP64的封装不同,在WLCSP封装上没有PC3,但提供了VREF+引脚。

7. 此类复用功能能够由软件配置到其他引脚上(如果相应的封装型号有此引脚),详细信息请参考STM32F10xxx参考手册的复用功能I/O章节和调试设置章节。

8. LQFP64封装的引脚5和引脚6在芯片复位后默认配置为OSC_IN和OSC_OUT功能脚。软件可以重新设置这两个引脚为PD0和PD1功能。但对于LQFP100/BGA100封装和LQFP144/BGA144封装,由于PD0和PD1为固有的功能引脚,因此没有必要再由软件进行重映像设置。更多详细信息请参考STM32F10xxx参考手册的复用功能I/O章节和调试设置章节。

9. LPFP64封装的产品,没有FSMC功能。

译注:

表中的引脚名称标注中出现的ADC12_INx(x表示4~9或14~15之间的整数),表示这个引脚可以是ADC1_INx或ADC2_INx。例如:ADC12_IN9表示这个引脚可以配置为ADC1_IN9,也可以配置为ADC2_IN9。

同样,表中的引脚名称标注中出现的ADC123_INx(x表示0~3或10~13之间的整数),表示这个引脚可以是ADC1_INx或ADC2_INx或ADC3_INx。

表中的引脚PA0对应的复用功能中的TIM2_CH1_ETR,表示可以配置该功能为TIM2_TI1或TIM2_ETR。同理,PA15对应的重映射复用功能的名称TIM2_CH1_ETR,具有相同的意义。

- stm32f103zet6引脚图(09-12)

- 马达控制驱动芯片l9110引脚图及l9110引脚定义(08-20)

- adc0809引脚图及功能详解,adc0809与51单片机连接电路分析(08-13)

- 详解555引脚图与内部功能结构(07-03)

- at89s52引脚图_at89s52引脚说明(09-20)