串行结构的FIR滤波器设计 (含有代码 文档资料)

一、功能描述

FIR滤波器,即有限脉冲响应滤波器,顾名思义,是指单位脉冲响应的长度是有限的滤波器。而根据FIR滤波器的结构形式,分为直接型、级联型、频率取样型和快速卷积型。其中直接型又可以采用串行结构、并行结构、分布式结构。本案例实现了具有线性相位的半串行结构的FIR滤波器。

所谓串行结构,即串行实现滤波器的累加运算,将每级延时单元与相应系数的乘积结果进行累加后输出,因此整个滤波器实际上只需要一个乘法器运算单元。串行结构还可以分为全串行和半串行结构,全串行结构是指进行对称系数的加法运算也由一个加法器串行实现,半串行结构则指用多个加法器同时实现对称系数的加法运算。

本案例设计了一个15阶的低通线性相位FIR滤波器,采用布莱克曼窗函数设计,截止频率为500HZ,采样频率为2000HZ;实现全串行结构的滤波器,系数的量化位数为12比特,输入数据位宽为12比特,输出数据位宽为29比特,系统时钟为16kHZ。采用具有白噪声特性的输入信号,以及由200HZ及800HZ单点频信号叠加的输入信号。

滤波器系数:12‘d0,-12’d3,12‘d15,12’d46,-12‘d117,-12’d263,12‘d590,12’d2047

二、平台效果图

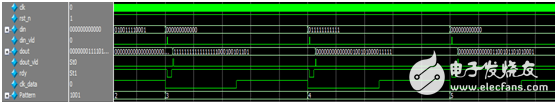

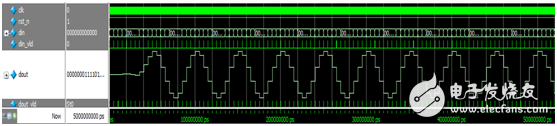

1.modelsim仿真效果图

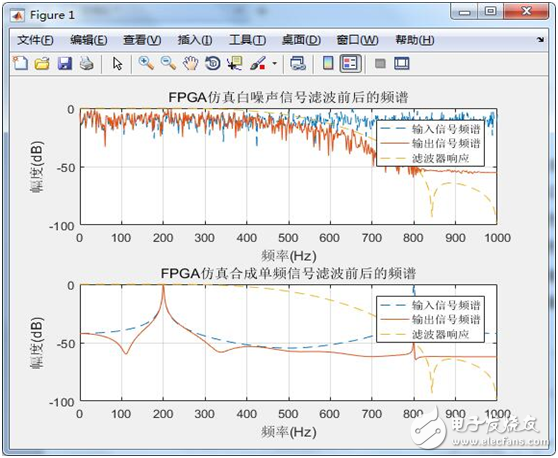

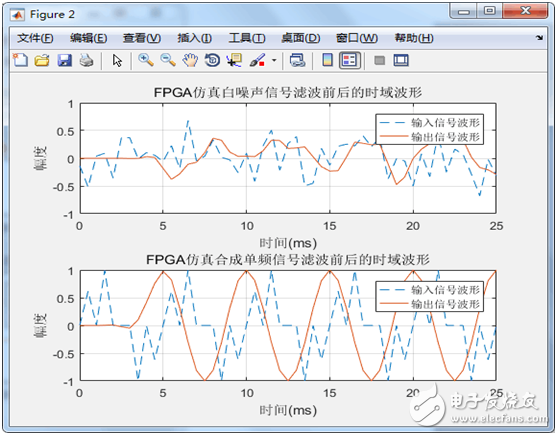

2.MATLAB效果图

三、实现过程

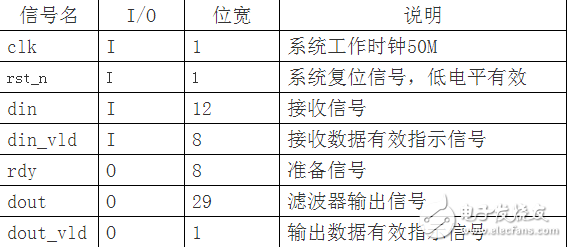

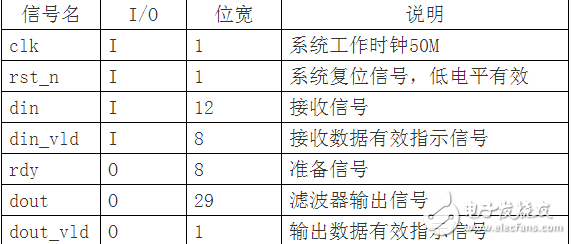

首先根据所需要的功能,列出工程顶层的输入输出信号列表。

我们可以把工程划分成三个模块,分别是FIR滤波器模块和加法器模块和乘法器模块。

1.FIR滤波器模块

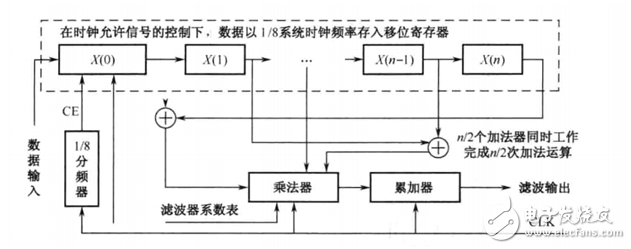

具有线性相位的半串行FIR滤波器结构图:

在时钟允许信号的控制下,将数据以1/8系统时钟频率存入16个移位寄存器中,然后将对称系数的输入数据相加,比如X(0)*X(N),X(1)*X(N-1),X(2)*X(N-2),同时将对应的滤波器系数送入乘法器中得到结果mult_s,再对此乘法结果进行累加sum 《= sum + mult_s,并输出滤波后的数据。

以此本模块实现了具有线性相位的半串行FIR滤波器功能。

本模块信号列表如下:

2.加法器模块

调用了Quartus II 里的加法器IP核,以实现FIR滤波器中的加法器模块。

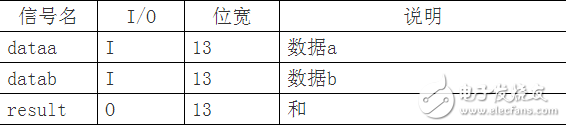

信号列表如下:

3.乘法器模块

调用了Quartus II 里的乘法器IP核,以实现FIR滤波器中的乘法器模块。

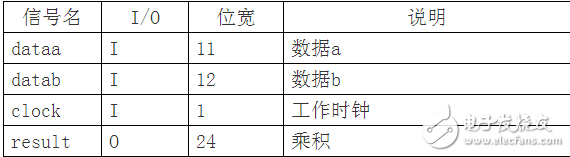

信号列表如下:

四、MATLAB部分说明

使用MATLAB设计出滤波器系数,仿真出滤波器测试数据、测试数据经滤波器滤波后的输出数据并转换成二进制数据写入文本文件中供Modelsim进行仿真。

编写MATLAB程序,从Modelsim仿真后生成的文本文件中读取滤波器输出数据,对数据进行时域及频域分析,程序运行结果见平台效果图。

代码资料下载

滤波器 相关文章:

- EMI噪声分析及EMI滤波器的设计(10-07)

- 单片机数字滤波的算法(10-12)

- 升压电源与高压天线和滤波器提供调谐信号(01-28)

- 自激式开关稳压电源的工作原理及功能设计(01-13)

- 充电电源怎么样轻松估计负载瞬态响应的方法(04-18)

- 浅析直流电源滤波电路及电子滤波器原理(09-21)