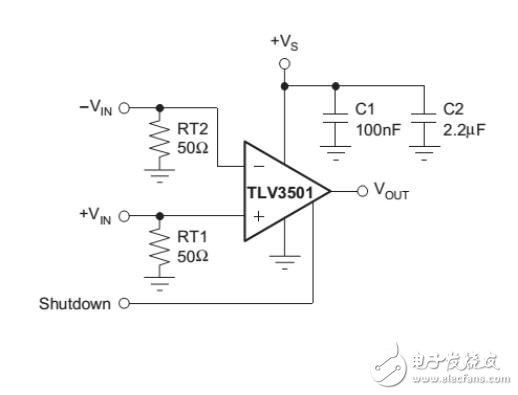

TLV3501应用电路及其电路图

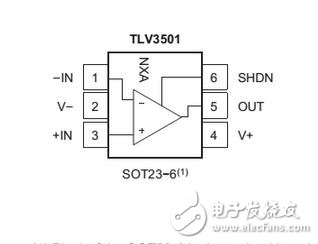

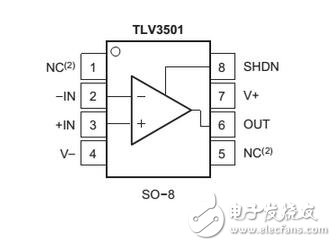

TLV3501管脚/引脚配置:

SO—8:脚1:NC

脚2:反相输入端

脚3:同向输入端

脚4:负电源输入端

脚5:NC

脚6:输出端

脚7:正电源输入端

脚8:关断信号控制端

对于SOT23-6封装由上图可以看出引脚1是由定向的包装标记。 SO-8比SOT23-6封装多了两个NC引脚,NC引脚为空脚,没有内部的电路连接。

TLV3501应用电路:

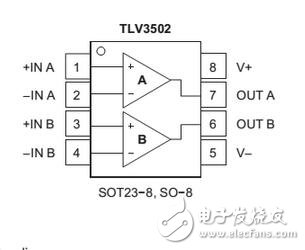

TLV3501和TLV3502均配备高速响应,包括内部的滞后,以提高抗噪性能与扩展0.2V超出电源轨的输入共模范围为6mV。

关断

一个停机引脚允许器件进入空闲状态时,它是不使用。当关断引脚为高电平时,芯片的电流大约为2μA,输出变为高阻抗。当关断引脚为低电平时,TLV3501是有效的。当不使用TLV3501关机功能,只需连接关断引脚到最负电源,如图1。大约需要100ns的走出来的关断模式。该TLV3502不具备关断功能。

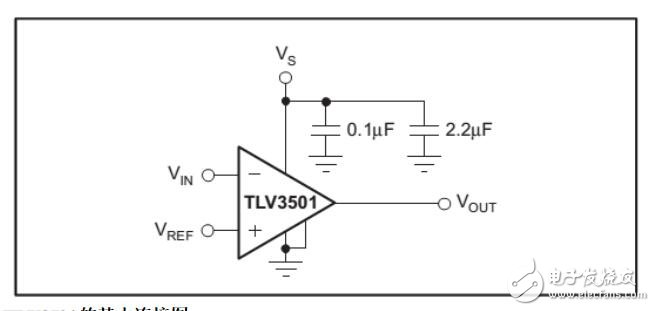

TLV3501应用电路图

工作电压

TLV3501比较器用于指定从+2.7V至+5.5 V单电源(或±1.35V双电源至±2.75V)在-40°C至+125°C的温度范围内时芯片运行低于这个范围时不是特定的性能。

增加外部迟滞

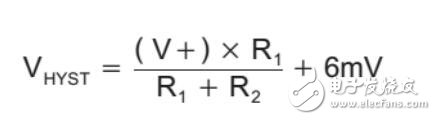

该TLV350x拥有强劲的性能与良好的布局使用性。然而,比较器输入具有指定的偏移电压(±5mV的)范围内的小抗干扰能力。对于缓慢移动的或有噪声的输入信号时,比较器输出可以显示多个开关作为输入信号移动的开关阈值。在这种应用中,TLV350x的内部迟滞的可能为6mV或更大。在更大的抗噪性需要的情况下,外部滞后可通过添连接少量的反馈到正输入。图2显示了用于引入额外的滞后为25mV,共计31mV滞后5V单电源供电时的典型拓扑。总滞后是由下式

切换比较器的输出所需要的转变电压的值,通过增大阈值区域,从而降低噪声干扰。

过电压保护

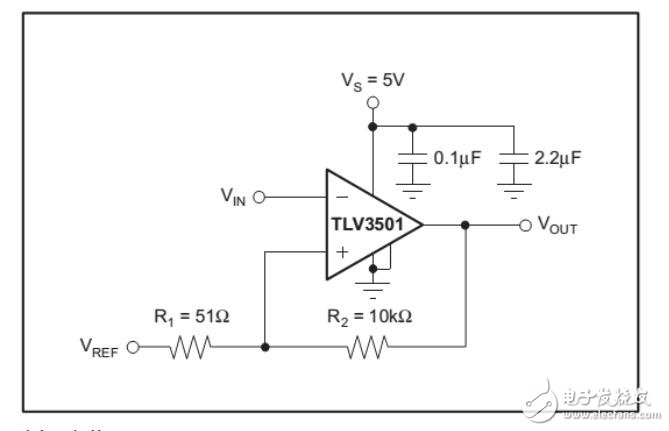

芯片的输入会通过"静电外释"二极管,如果输入电压超过电源约300mV时将受到保护。瞬时电压大于电源300mV是可以的,可以通过串联一个小的电阻到芯片,将输入电流限制在10mA,如图3。

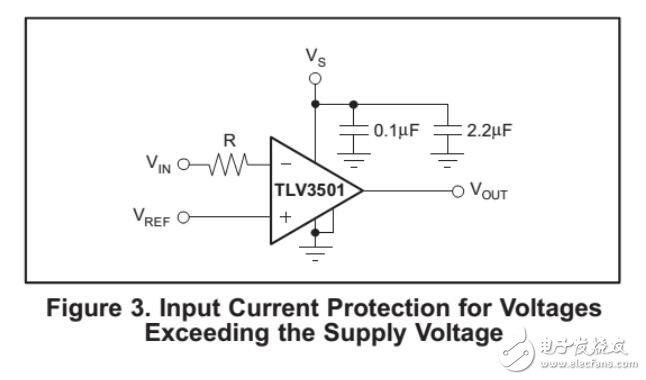

振荡器

TLV350x可以很容易地配置为简单和廉价的弛张振荡器。在图4中,R2的网络设置在三分之一到三分之二的跳闸阈值。因为这是一个高频电路,电阻器的值是相当低,以最小化电容的影响。三分之一的V +的三分之二之间的正输入端候补取决于输出是否低或高。充电时间(或放电)是0.69R1C。因此,该期间是1.38R1C。为62pF和图4中所示1kΩas,输出被计算为10.9MHz。这种电路的一个实施振荡在9.6MHz。寄生电容和元件容差讲解理论与实际性能之间的差异

PCB布局

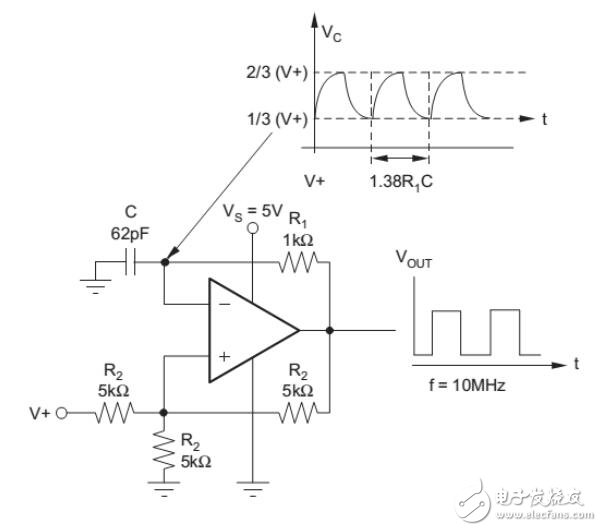

对于任何高速比较器或放大器,正确的设计和印刷电路板(PCB)布局可以让芯片达到最佳性能。有源输入如果增加多余电容或不正确的接地,会限制高速比较器的最大性能。从信号源到比较器的输入电阻最小化是必要的,以便最大限度地减少整个电路的传播延迟。随着输入电容的源电阻产生的RC滤波器,延迟电压变化在输入,并降低了高频信号的振幅该TLV350x随着从输入引脚的电容至地的结果在几个电容皮法。

用于电源旁路电容的位置和类型是高速比较器的关键。建议的2.2μF钽电容器不需要像靠近器件为0.1μF的电容,并且可以与其他设备共享。该2.2μF电容缓冲对纹波电源线和0.1μF的电容提供高频时转换为比较器的开关。 在高频电路中,对于直流在相同的电位快速的上升和下降电压差可以看做一个瞬态开关,为了减少这种影响,一个接地平面通常被用来减小电路板内的电压电位差。一个接地平面具有降低对电路板寄生电容的影响的优点,通过提供一种更可取的路径的电流流过。有超过一个接地平面上的信号迹线,在高频率的返回电流(在接地平面)的倾向右下的信号路径流动。接地平面(如简单的通孔引线和通孔)增加平面的电感,使得在较高频率上它不那么有效。在地平面上进行必要的休息过孔应随机分布。

- TLV3501怎么做比较器,TLV3501比较器电路设计思路(07-08)

- TLV3501过零比较器电路设计(07-08)

- TLV3501比较器电路原理图、参数封装与应用(07-08)

- TLV3501滞回比较器电路设计(07-08)

- TLV3501比较器电路设计:交流耦合单电源比较器(07-08)

- 一种CMOS绿色模式AC/DC控制器振荡器电路(09-16)