数字频率正弦信号发生器控制电路

直接数字频率合成DDS(Direct Digital Syndaesis)是实现数字化的一项关键技术,广泛应用于电信与电子仪器领域。DDS 通常是在CPLD 或FPGA 内设置逻辑电路实现的,但由于DDS 输出受到D/A 转换器的速率及D/A 转换后I/V 转换中运放的带宽增益和响应时间的限制,CPLD 和FPGA 内部实现方案在高频段信号幅值已不稳定。因此,这里介绍一种基于DDS 器件AD9851的信号发生器设计方案。

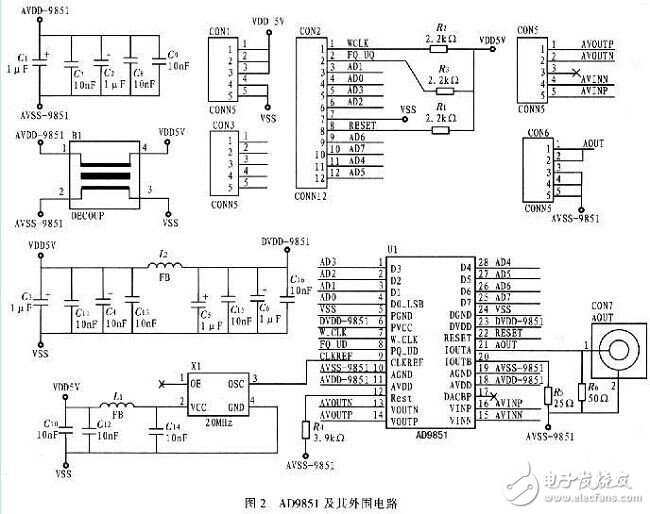

AD9851电路模块和控制逻辑

由于AD9851工作频率较高,容易引入较大噪声,因此需要注意电源与地线的连接,以减小噪声。为避免高频干扰,用PCB 制板实现AD9851及其外围。其电路如图2所示。

频率控制字和相位控制字写入时序有并行和串行两种方式,这可用PFGA 内部状态机实现。该系统设置的FM 调制分为两级最大频偏:5kHz 和10kHz,而PSK 调制信号由改变相位控制字实现。控制字及理论值计算如下:低频段DDS 波表输出数据为14位(214=16,384)。PSK 控制字在DDS 波表输出值大于16,384/2=8,192时,改变相位180°。由于AD9851相位控制字为高5位,故若改变180°则改变相位控制字8’h90。AD9851的最高输出150MHz 对应频率控制字32’hFFFFFFFF(十六进制),故1Hz 对应28.633,1(十进制)。

正弦信号发生器的信号输出范围达100Hz~lOMHz,频率稳定度优于10-4,幅度稳定可调,同时可输出各种常用调制信号,并具有即时频率转换、控制灵活、幅度稳、体积小、成本低等优点,使得该系统能够在各种便携领域用作信号源。积小、成本低等优点,使得该系统能够在各种便携领域用作信号源。

- 低频正弦信号发生器的设计(02-15)

- 一种新型的正弦信号发生器的设计与实现(04-23)

- 什么是OpenCL?面向FPGA的OpenCL有何优点?(03-12)

- 准确理解优先级才是管理过冲的一剂良药(10-18)

- FPGA数字变换器控制电路设计攻略(02-03)

- 浅谈低功耗控制电路和程序设计思路(10-13)