揭秘FPGA多重配置硬件电路设计方案

现代硬件设计规模逐渐增大,单个程序功能越来越复杂,当把多个功能复杂的程序集成到一个FPGA 上实现时,由于各个程序的数据通路及所占用的资源可能冲突,使得FPGA 控制模块的结构臃肿,影响了整个系统工作效率。通过FPGA 的多重配置可以有效地精简控制结构的设计,同时可以用逻辑资源较少的FPGA 器件实现需要很大资源才能实现的程序。以Virtex5系列开发板和配置存储器SPI FLASH 为基础,从硬件电路和软件设计两个方面对多重配置进行分析,给出了多重配置实现的具体步骤,对实现复杂硬件设计工程有一定的参考价值。

当FPGA 完成上电自动加载初始化的比特流后,可以通过触发FPGA 内部的多重启动事件使得FPGA 从外部配置存储器(SPI FLASH)指定的地址自动下载一个新的比特流来重新配置。FPGA 的多重配置可以通过多种方式来实现。

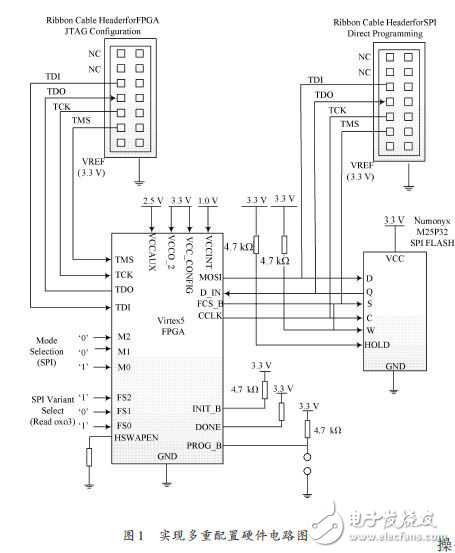

电路原理:多重配置的硬件主要包括FPGA 板卡和贮存配置文件的FLASH 芯片。FPGA 选用XILINX 公司Virtex-5系列中的ML507,该产品针对FPGA 多重配置增加了专用的内部加载逻辑。FLASH 芯片选用XILINX 公司的SPI FLASH芯片M25P32,该芯片存贮空间为32 Mb,存贮文件的数量与文件大小以及所使用的FPGA 芯片有关。实现多重配置首先要将FPGA 和外部配置存储器连接为从SPI FLASH 加载配置文件的模式。配置电路硬件连接框图如图1所示。在FPGA 配置模式中,M2,M1,M0为0,0,1,这种配置模式对应边界扫描加上拉,FPGA 在这种模式下所有的I/O 只在配置期间有效。在配置完成后,不用的I/O 将被浮空M2,M1,M0 三个选择开关对应于ML507 开发板上的SW3开关中的4,5,6位,在FPGA 上电之前将上述开关拨为0,0,1状态。

- 下一代Flash存储器在工业控制领域技术与应用(02-05)

- 闪迪瞄准汽车与工业领域 推出相应存储解决方案(04-04)

- 攻克可穿戴医疗存储器件封装难题(09-23)

- FPGA中SPI Flash存储器的复用编程方法的实现(09-13)

- 为何电子式电能表需要使用铁电存储器(F-RAM)(09-11)

- 铁电存储器的技术特点分析(09-18)