嵌入式系统中的USB总线接口电路图

详细阐述了一种用于嵌入式系统中的USB总线接口电路,该电路是基于USB专用芯片CH375实现的,并给出了系统硬件实现和应用程序。实验结果表明,该电路具有成本低、可靠性高等特点,可方便地集成到各种嵌入式系统中。

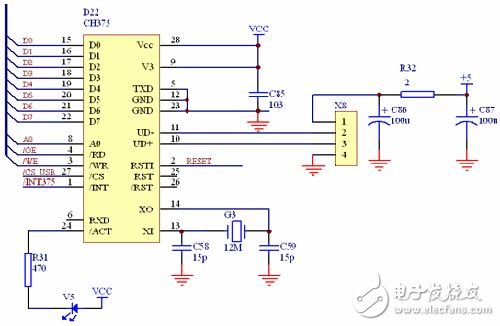

接口电路设计:单片机与CH375芯片的连接方式有串行接口和并行接口两种,串行接口连接方式虽然电路连接简单,不用扩展使用外部地址空间,但其要遵循一定的通信协议,软件设计较为复杂,并且传输速度较并行接口的传输速度要慢。对于大多数嵌入式系统应用,因串口资源较少,而且扩展外部地址空间技术非常成熟,故本接口电路采取了并口连接方式。其电路原理图如图2所示。

图2 接口电路图

图2中的X8为USB接口插座,为了避免USB设备接入嵌入式系统时,工作电流突然加大,干扰嵌入式系统的正常运行。在设计电路时,在靠近 USB接口插座的位置加了一个2欧姆的限流电阻,用于防止USB设备接入时电流过载;同时,在USB接口插座电源处加上一个100μF的电解电容,用于储能和滤波,提高USB端口的带载和抗干扰能力。

图2中CH375的复位端(RSTI)与嵌入式系统复位信号(RESET)连接,从而保证嵌入式系统复位时CH375能同步复位;发送端 (TXD)决定芯片的工作方式,该引脚内置弱上拉电阻,在复位期间输入低电平则使能并口,悬空或输入高电平则使能串口,本接口电路工作在并口方式,图中发送端(TXD)直接接地;晶体振荡的输入端(XI)和反相输出端(XO),外接12MHz的晶体及2个15pF的振荡电容,为芯片提供工作时钟;8位双向数据总线(D0-D7)直接与嵌入式系统的低8位数据总线连接,用于两者间的数据交换。读选通输入端(/RD)、写选通输入端(/WR)、中断请求输出端 (/INT)分别与嵌入式系统的读信号(/OE)、写信号(/WE)和外部中断输入端(/INT375)连接;片选控制输入端(/CS)与嵌入式系统中译码器输出端(/CS_USB)连接;地址线输入端(A0)用于区分命令口与数据口,与系统地址线A0连接,以上控制信号用于控制芯片按照正确的时序工作。电路的其他一些电容主要用于电源的退藕和滤波,不再一一详叙。

- 嵌入式系统在电源设计中的运用(09-20)

- 基于4G通信的嵌入式数据通信系统设计(10-10)

- 汽车安全性能亟待升级 嵌入式系统把关护航(05-07)

- USB端口找到新居,落户嵌入式系统(02-11)

- 嵌入式系统在电力变压器监测中的应用研究(09-18)

- 基于OMAP架构的嵌入式指纹识别系统设计与应用(04-29)