在FPGA开发中尽量避免全局复位的使用?(4)

时间:02-11

来源:网络整理

点击:

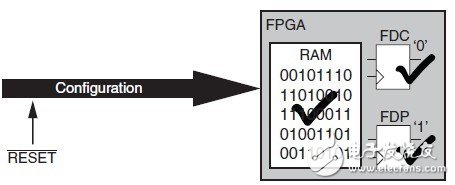

如何自动覆盖99.99%的情况

随着Xilinx的FPGA芯片越来越多的嵌入处理器内核,比如MicroBlaze软核、ARM和PowerPC硬核等,这种特性使得所有的程序和数据空间在处理器内核执行第一条指令之前都已经被预定义,则原来那种靠烧写昂贵的可编程资源来仅仅复位触发器的操作变得毫无意义了。开发过程中所使用的仿真工具也应当具有模拟此操作的能力(即我们通常所说的"上电复位"),这样在后续的设计中就可以避免使用可有可无的复位操作了。

其余0.01% 情况的设计准则

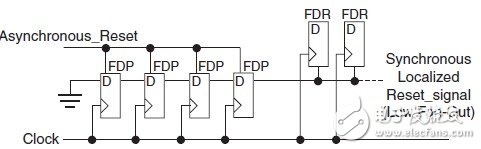

最重要的事情是使用某些准则来处理设计中的复位操作,并且这些准则在设计审查阶段就应该被完全考虑到。可以使用一个局部的高性能的复位网络来控制仅仅需要局部复位的触发器。图7给出了一个这种局部复位的示意图。这种电路的优点在于,它所提供的复位效果与外接全局复位信号的效果是一致的。

图7 局部复位示意图

在器件配置或者异步复位时,链中的所有触发器都被预设为1。几乎在这同时,链中的最后一个触发器驱动局部复位网络并向其发送一个有效复位信号。随着全局复位/置位信号或异步复位信号的释放,整个移位寄存器链开始在每个时钟周期被填充为0。链中触发器的数目决定了局部复位网络所需要的复位脉冲的最小宽度。最后的结果是,链中最后一个触发器从高跳变到低,而局部复位信号的释放与时钟周期同步。被复位的触发器可以采用同步置位(synchronous set (FDS))或者同步复位(synchronous reset (FDR)),即构成了完整的同步设计,而接下来的时序规范和分析也将容易得多。

- Xilinx Kintex UltraScale 一半尺寸的 PCI Express 平台 (HTG-K816)(06-15)

- Xilinx全新参考设计提供业界首个单芯片400G解决方案(02-12)

- Xilinx用于工业自动化的机器视觉解决方案(11-30)

- Xilinx多协议机器视觉摄像机参考设计(12-01)

- 机器视觉技术原理解析及解决方案集锦(02-06)

- 机器视觉在汽车电子方向的应用解决方案(02-13)