Xilinx可编程逻辑器件设计与开发(基础篇)连载7:Spartan

时间:02-11

来源:网络整理

点击:

时钟布线资源具有高速、低SKEW的特点,它对系统设计非常重要,即使系统速率不高,也应该关注时钟设计,以消除潜在的时钟危险。Spartan-6器件包含16个全局时钟资源和40个I/O区域时钟资源。全局时钟用于系统时钟,而I/O区域时钟专用于I/O串行/解串(ISERDES和OSERDES)设计。

Spartan-6时钟资源包含以下4种。

全局时钟输入引脚(GCLK)。

局时钟多路复用器。

I/O时钟缓冲器。

时钟布线网络。

包括由BUFGMUX驱动的全局时钟网络和由I/O时钟缓冲器(BUFIO2)、PLL时钟缓冲器(BUFPLL)驱动的I/O区域时钟网络。

一、 时钟输入

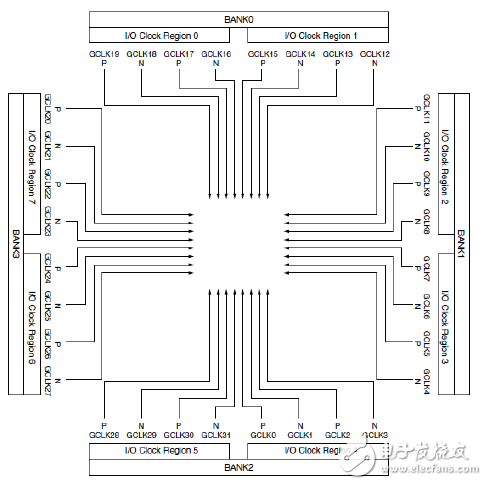

每个Spartan-6有32个全局时钟输入引脚,分布在FPGA的四周。时钟输入引脚在片上的分布图如图2-5所示。时钟输入引脚接收外部时钟信号,直接连接片内的DCM/PLL/BUFGMUX/BUFIO2。时钟输入引脚不连接时钟时,用作普通I/O。

一个差分时钟输入需要两个全局时钟输入。成对的时钟输入在标号上是连续的,例如,GCLK0和GCLK1是差分对,GCLK20和GCLK21是差分对。每个全局时钟缓冲器有两个时钟输入,Spartan-6支持最多16对的差分全局时钟输入。

设计中的时钟输入引脚连接IBUFG原语,通常综合工具会分析设计,自动将顶层时钟引脚推演为与IBUFG相连。如果需要更多IBUFG的控制功能,可以通过例化IBUFG的方式,将IBUFG的I端口连到顶层端口,将O端口连接到DCM、BUFG或通用逻辑。

图2-5 时钟输入引脚片上分布图

- 可编程逻辑控制器(PLC)基本操作及功能简介(03-07)

- 基于可编程逻辑器件的数字电路设计(10-16)

- 基于CPLD的机载雷达控保系统设计与实现(10-29)

- 德州仪器可编程逻辑和自动化控制器(PLC/PAC)解决方案(11-03)

- 基于Xilinx(赛灵思) CPLD的看门狗电路设计(10-09)

- 莱迪思技术专家分享:基于FPGA的视频监控时代(02-21)