Xilinx可编程逻辑器件设计与开发(基础篇)连载8:Spartan

二、 全局时钟缓冲器/多路复用器

Spartan-6的时钟缓冲器/多路复用器(BUFG或BUFPLL)可以直接驱动时钟输入信号到时钟线上,或者通过多路复用器在两个不相关的信号甚至异步时钟信号中切换。

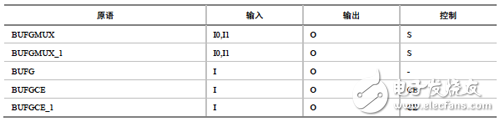

全局时钟缓冲器的原语如表2-7所示。

表2-7 全局时钟缓冲器/多路复用器的原语

(1) BUFGMUX。

BUFGMUX可以作为一个BUFG,或者作为两个全局时钟源的多路选择器在两个时钟源之间切换。BUFGMUX只驱动全局时钟布线资源。通用布线资源也能驱动FPGA逻辑触发器上的时钟输入,但是通常不推荐使用,因为通用布线资源有较高的SKEW。

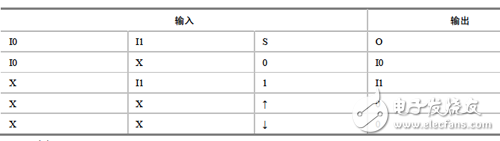

如图2-6所示,BUFGMUX是具有两个时钟输入I1 和I0、一个时钟输出O和一条选择线S的时钟缓冲器,可以消除两个时钟源之间切换时产生毛刺信号。选择线S必须满足建立时间要求,违反这一建立时间可能导致毛刺信号。

选择线S翻转选择另一个时钟源输出时,输出保持在一个非活动态直到下一个有效时钟沿到来。当两个时钟切换时,输出电平可以为高电平或低电平,缺省为低电平。交叉解耦寄存器确保了BUFGMUX 输出不会产生一个时钟脉冲边沿。

当S输入改变时,输出保持为Low,直到另一(待选)时钟从High 转为Low。然后,新的时钟开始驱动输出,如表2-8 所示,由于输入第一个低到高的跳变输出不翻转,所以,输出不会比最短输入时钟脉冲短。

S输入为低,选择时钟输入I0;S输入为高,选择时钟输入I1。BUFGMUX还具有内置可编程极性,等效于交换I0和I1。每个触发器可以对时钟信号进行极性设置,确定上升沿或下降沿触发,避免产生两个不同的时钟信号。

表2-8 BUFGMUX功能表

(2) BUFGMUX_1。

BUFGMUX_1和BUFGMUX功能相同,区别在于BUFGMUX_1对上升沿敏感,并且在输入切换之前保持为High。

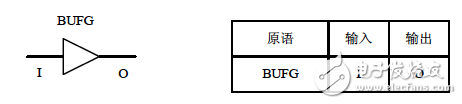

(3) BUFG。

如图2-7所示,BUFG其实就是具有一个时钟输入和一个时钟输出的时钟缓冲器,它也是Virtex 和Spartan器件中时钟缓冲器的通用原语。

图2-7 BUFG的原语

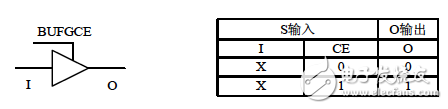

(4) BUFGCE 和BUFGCE_1。

BUFGCE是具有一个时钟输入、一个时钟输出和一条时钟使能线的时钟缓冲器。当时钟使能CE为高,输入I 经缓冲器输出;当CE为低(非激活状态),输出O为低。其原语如图2-8所示。

图2-8 BUFGCE的原语

BUFGCE_1与BUFGCE功能相同,不同的是,当时钟使能CE为低时,输入I 经缓冲器输出;当CE为高(非激活状态),输出O为高。

- 基于Xilinx Spartan-6 FPGA加速纹理映射的实现(09-08)

- Xilinx Spartan-3系列FPGA的配置电路(05-01)

- 赛灵思关于Spartan-3E的低成本显示器解决方案(06-30)

- 骨灰级音响发烧友如何打造随身DAC兼耳扩?(02-09)

- 6 FPGA LX9 MicroBoard成为学习FPGA的另一低成本方法(02-10)

- Spartan6开发中bufpll mapping error(02-11)