Xilinx可编程逻辑器件设计与开发(基础篇)连载9:Spartan

三、 I/O 时钟缓冲器

除了全局时钟缓冲器外,Spartan-6还包含驱动高速I/O时钟区域的时钟缓冲器。

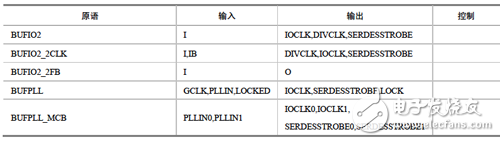

I/O 时钟缓冲器的原语如表2-9所示。

表2-9 I/O时钟缓冲器的原语

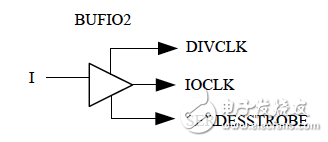

(1) BUFIO2。

BUFIO2接收来自GCLK时钟输入,产生两个时钟输出和一个驱动IOSERDES2的选通脉冲,如图2-9所示。

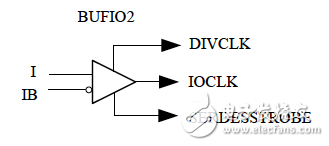

(2) BUFIO2_2CLK。

BUFIO2_2CLK和BUFIO2功能几乎相同,不同的是BUFIO2_2CLK的输入为两个单端时钟或者一对差分时钟(IBUFDS_DIFF_OUT 的输出),如图2-10所示。

图2-9 BUFIO2的原语

图2-10 BUFIO2_2CLK的原语

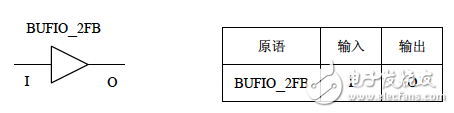

(3) BUFIO_2FB。

BUFIO2FB 是一个单输入单输出的缓冲器,有一个输出属性控制输出延时,如图2-11所示。当属性divIDE_BYPASS 设置为TRUE时,BUFIO_2FB等同于BUFIO2旁路延时;

当属性divIDE_BYPASS设置为FALSE时,BUFIO_2FB的延时与BUFIO2 的divCLK输出类似,保持BUFIO2的输出和BUFIO_2FB相位对齐。

图2-11 BUFIO_2FB的原语

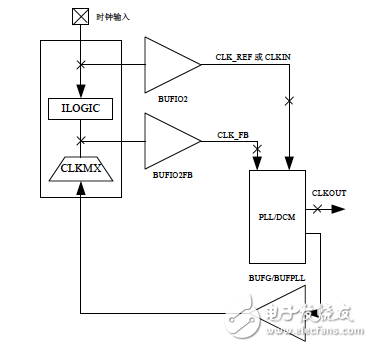

BUFIO_2FB缓冲器为CMT(PLL或DCM)参考输入CLKIN和反馈输入CLKFB的时钟布线延时提供了一个很好的解决方法。当使用CMT的反馈路径时,ISE会自动插入BUFIO_2FB和BUFIO2缓冲器,如图2-12所示。

图2-12 BUFIO_2FB 缓冲器与时钟布线延时匹配

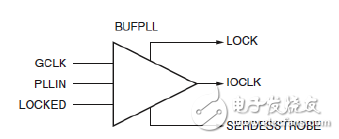

(4) BUFPLL。

图2-13所示为BUFPLL的原语,主要用来驱动高速I/O,为ISERDES2和OSERDES2提供时钟。

它会将PLL的LOCK输出与GCLK、SERDES选通和PLL时钟对齐。其中的IOCLK仅仅是将输入时钟通过了一级缓冲的版本。LOCK输出信号其实与PLL的LOCKED信号具有相同的功能,它们的区别在于,在PLL 锁定、BUFPLL对齐SERDES选通信号之前,LOCK不会变高。

图2-13 BUFPLL的原语

Spartan-6器件每个BANK有两个BUFPLL,专用于PLL,不建议将其用作逻辑时钟。

(5) BUFPLL_MCB。

BUFPLL_MCB专用于Spartan-6内集成的存储器控制器。详细描述请参考附带光盘中的《Spartan-6存储器控制器用户手册》。

- 可编程逻辑控制器(PLC)基本操作及功能简介(03-07)

- 基于可编程逻辑器件的数字电路设计(10-16)

- 基于CPLD的机载雷达控保系统设计与实现(10-29)

- 德州仪器可编程逻辑和自动化控制器(PLC/PAC)解决方案(11-03)

- 基于Xilinx(赛灵思) CPLD的看门狗电路设计(10-09)

- 莱迪思技术专家分享:基于FPGA的视频监控时代(02-21)