pcb设计信号失真常被忽视的来源——过孔

多年以来,工程师们开发了几种方法来处理引起PCB设计中高速数字信号失真的噪音。随着设计技术与时俱进,我们应对这些新挑战的技术复杂性也日益增加。目前,数字设计系统的速度按GHz计,这个速度产生的挑战远比过去显著。由于边缘速率以皮秒计,任何阻抗不连续、电感或电容干扰均会对信号质量造成不利影响。尽管有各种来源会造成信号干扰,但一个特别而时常被忽视的来源就是过孔。

简单过孔中的隐患

高密度互连(HDI)、高层数印刷电路板和厚背板/中间板中的过孔信号会受到更多抖动、衰减和更高误码率(BER)的影响,导致数据在接收端被错误解释。

以背板和子卡为例。当遇到阻抗不连续时,焦点在于这些板子与母卡之间的连接器。通常情况下,这些连接器在阻抗方面非常匹配,不连续实际源自过孔。

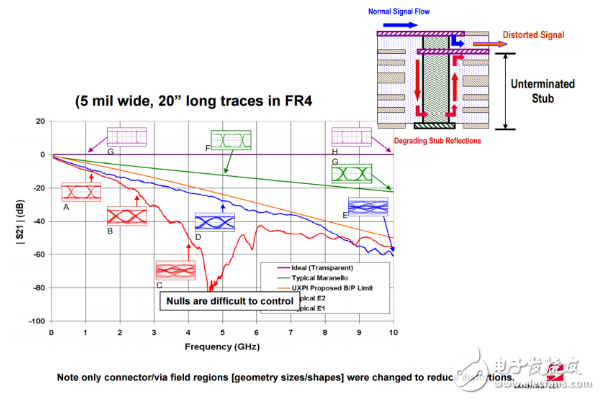

随着数据速率的增加,由镀通孔(PTH)过孔结构引起的失真量也会增加——通常以远高于相关数据速率增量的指数级速率增加。例如,一个PTH过孔在6.25Gb/s时的失真通常比在3.125Gb/s时产生的失真大两倍以上。

在底层和顶层出现的不需要的过孔残段延伸层,使过孔显示为较低的阻抗不连续性。工程师们克服这些过孔额外电容的一个方法是,将其长度最小化,从而减小其阻抗。这就是背钻的由来。

长过孔残段信号失真[1]

使用背钻技术

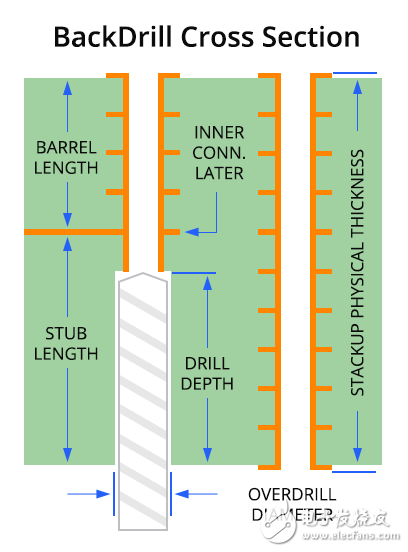

通过清除过孔残段,背钻已被广泛认为是把通道信号衰减降到最低程度的简单而有效的方法。该技术被称为定深钻孔,它采用传统的数控(NC)钻孔设备。同时,该技术可应用于任何类型的电路板,而不只是像背板一样的厚板。

相对于原始过孔,背钻法使用的钻头直径稍大,以便移除不需要的导体残段。该钻头通常比主钻规格大8mil,但许多制造商都能满足更严格的规格。

需要记住的是,距离走线与平面的间距需要足够大,以保证背钻程序不会穿透附近的走线和平面。为避免穿透走线和平面,建议间距为10mil。

一般而言,通过背钻减少过孔残段的长度有许多好处,包括:

按数量级降低确定性抖动,使得误码率更低。

通过改善的阻抗匹配降低信号衰减。

降低来自残段的电磁干扰/电磁兼容性辐射,并增加通道带宽。

降低共振励磁模式和过孔间串扰。

以比顺序层压法更低的制造成本,将设计和布局影响降到最低。

背钻横截面

通过背钻沟通设计意图

随着背钻技术在高密度互连和高速设计应用中的频繁使用,此方法也带来了可靠性问题。其中一部分问题包括缺乏设计指南、制造公差、以及如何确保将设计意图良好地传达到制造单位。

那么,如何确保您的制造商拥有背钻目标过孔和镀通孔元件需要的所有信息?如何保持跟踪整个设计过程中背钻规格的多个级别?

其实需要的东西非常简单:集成到设计规则中的简单可视化配置工具,使您能为所选对象指定不同的背钻配置。然后,就可以让了解哪些过孔需要背钻的软件来帮您干活了。

参考文献:

[1] Dudnikov、George和Vladimir Duvanenko。"线路板和背板内更高速带宽传输的匹配端接残段过孔技术"。所有商标和注册商标均由各自所有者持有。摘要(未注明日期):无页码。线路板和背板内更高速带宽传输的匹配端接残段过孔技术。Sanmina – SCI,2008年。网络发布。2016年9月9日。

- 教你如何抵消OFDM系统的失真(02-12)

- 汽车电子控制器(ECU)的硬件设计流程(09-17)

- 高手告诫:印制pcb设计成功的七大技术要决(07-02)

- PCB设计是让产品成功的最重要关键(11-07)

- PCB设计的径向网格?谁这么有才!(04-22)

- 电池充电器电路的PCB设计(06-24)