FinFET存储器的设计挑战以及测试和修复方法

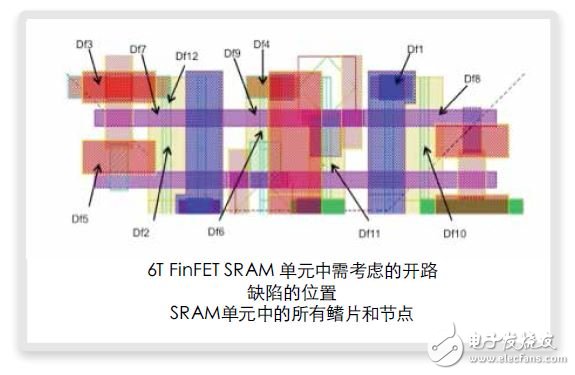

注入继续进行。这基于GDS (版图)本身。缺陷注入在版图和SPICE模型上进行,使用了针对每个库的缺陷库,然后观察它们会如何表现。缺陷注入在所有14/16nm FinFET提供商的晶体管上进行,不论是IDM还是代工厂。缺陷注入也在较高节点(如45nm和28nm)的平面工艺上进行。

图7:FinFET存储器单元版图中注入的开路缺陷实例

缺陷注入展示了每种缺陷的行为方式。接下来的任务就是通过测试序列识别(TSI)找到检测缺陷的测试序列。对于每种潜在的缺陷,一个或多个测试序列得以识别,同样其检测的条件及对应的故障模型也被确定。通常需要使用大量的测试序列、应力角和模拟设置,直至找出一个能明显区别于零缺陷单元的序列。

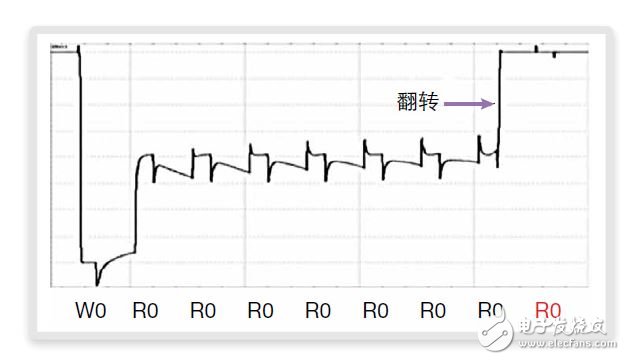

有些情况下,这些缺陷会是以前在平面工艺中见过的故障模型,但FinFET存储器有几种额外的失效模式。比如,图8给出了一种微妙的失效模式。下拉晶体管中的电阻性鳍片开路导致动态伪读破坏故障(dDRDF)。在此,一个写操作,接着7个读操作,导致存储器单元的位值翻转。然后可以更加详细地分析此故障,因为它原来与频率有关。在1.2MHz频率上,产生这个故障仅用了4次读操作,而在4MHz上,则用了18次读操作。温度和电压也会影响这些值。

图8:缺陷注入调查结果:dDRDF-7

来自Synopsys关于FinFET工艺故障建模的部分普遍结论是:

FinFET存储器比平面存储器对动态故障更敏感

FinFET存储器对制程变异故障更稳定

静态单单元和耦合故障在两种存储器中均很常见

应力角(电压、温度、频率)对于检测FinFET故障非常重要,仅使用标称角会遗漏一些问题。

生成测试序列

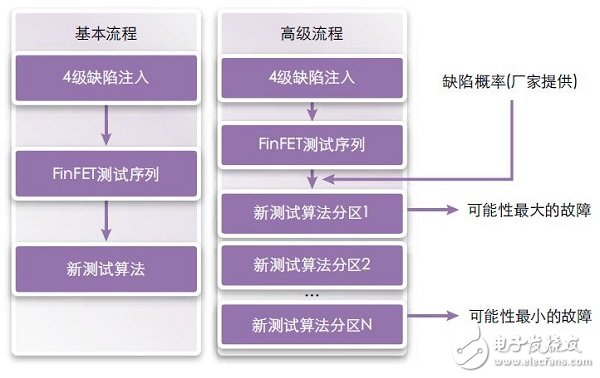

故障建模背景完成后,设计人员要明确测试的电压、温度和频率要求。给定应力角的序列与称为测试算法发生器(TAG)的引擎结合。TAG 将与针对个别故障类型的小测试序列组合在一起,产生使测试时间和测试成本最小化的最小测试算法。

图9展示了针对FinFET的TAG。图中的过程是全自动的,从故障注入到测试序列识别再到TAG本身。不同的算法片段可以分割以应对不同的应力角和不同的故障检测级别。分割形成了一个针对不同条件的测试序列池,这是由于不同用户和应用具有不同的要求。比如,生产测试期间,设计人员必须识别故障,以便他们能够纠错,但是确定每个故障根源的完整分析可能十分耗时。然而,如果某种错误经常发生,设计人员会执行更加复杂而昂贵的测试,以缩小故障范围,从而能采取相应的纠错措施。

图9:FinFETs测试算法综合

这些过程和测试全部在STAR存储器系统中得以实现,考虑了来自大多数FinFET提供商的故障,这些故障在不同提供商之间具有很大的共性,尽管位单元彼此相差很大。

STAR存储器系统还将可编程能力纳入其中。可以通过JTAG端口和TAP控制器更新算法,修改测试序列本身或为调试和诊断而升级算法,或者就是简单的算法升级,甚至是在现场。

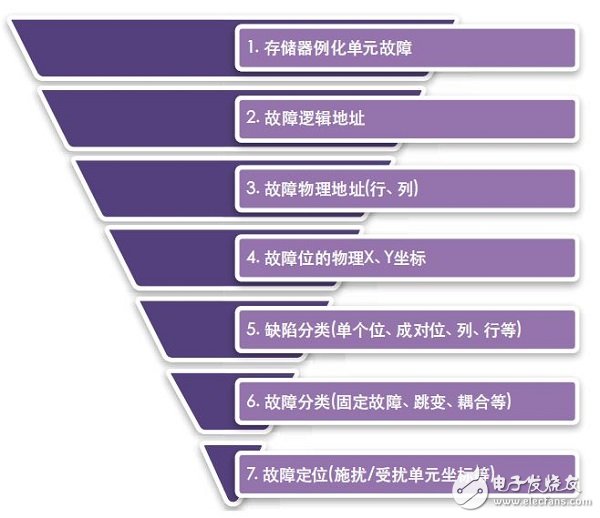

使用STAR存储器系统检测并修复故障

Synopsys对FinFET潜在故障和缺陷的深入而彻底的分析内建在了STAR存储器系统之中,使得该系统可以在很多层次上使用,如图10所示。最高层次是了解哪个存储器例化单元出现失效,这对于生产测试和纠错可能就足够了。下一个层次是故障的逻辑地址和物理地址。STAR存储器系统可以确定故障位的物理X、Y坐标。缺陷可以分类(单个位、成对位、整列等),故障可以分类并最终精确定位到故障部位。注意,所有这些都由芯片外面的STAR存储器系统确定,而不是使用电子显微镜或其他更精细/昂贵的方式。

图10:DesignWare STAR存储器系统:多层次精密诊断

开发为SoC用户(或存储器IP设计人员)带来高质量结果的工具和IP是一个漫长而持续的过程。从深入的存储器设计知识开始,早期接触多家代工厂的制程参数、大量的故障注入模拟、硅芯片特征化和精确的行为和结构模型,该过程可能需要三年以上。深入理解FinFET特有缺陷得到了对面积影响更小和测试时间更少的优化测试算法,外加对使缺陷易于显现的应力条件的认识。最后,所有这些知识全部结合在STAR存储器系统中用于创建自动插入、快速测试和使产出最大化。

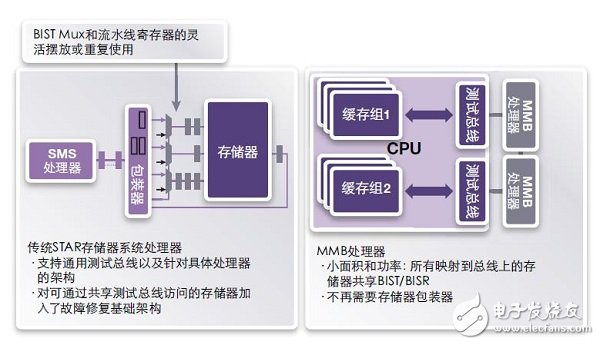

FinFET为使用预先插入的一组可调度的存储器优化时序提供了更多的可能性。BIST多路复用器可随共享测试总线落实到位。这些测试总线可由定制数据通路创建者和处理器内核进行复用。Synopsys创立了多存储器总线(MMB)处理器来充分利用FinFET提供的可能性。MMB与映射到该总线上的所有缓存共享BIST/BISR逻辑,因此不再需要存储器包装器,减小了面积占用和功率消耗(图11)。

图11:

- DE0-Nano-SoC 套件 / Atlas-SoC 套件(10-30)

- 高压电池组监视器可实现先进的电池系统(10-14)

- 如何最大化延长即使具有老化电池的汽车电池组运行时间(08-14)

- 高准确度 60V 电量计如何测量电量?(09-12)

- Cypress电容式触控元件出货量突破10亿颗(08-14)

- 瑞萨电子3大ADAS检测系统解决方案简述(02-08)