基于SOPC技术的多通道实时温度采集系统

模块的设计选用了PROFIBUS—DP专用通信协议芯片SPC3,这样可加速通信的执行,而且可以减轻微处理器的负担。

2.4 FPGA逻辑控制模块

基于FPGA的采集控制单元,采用自顶而下的模块化设计方法,使用Verilog HDL语言完成各控制模块的设计。FPGA逻辑控制模块包括A/D采样控制模块、FIFO读写控制模块和SPC3控制模块。

2.4.1 A/D采样控制模块

A/D采样控制模块负责控制外部ADS8402芯片多路模拟输入量的选通,并实现对A/D采样过程的合理控制。

由于ADS8402对16通道的模拟量采取分时转换的方式,因此在启动转换的同时还要进行通道选择。ADS8402设置了4根通道地址线A0、A1、A2、A3,以及地址锁存允许信号ALE。当ALE变高时,锁存由A0、A1、A2、A3编码所确定的通道号,将该通道的模拟量接入A/D转换器进行转换。依据这样的特性,设计一个带复位端的十六进制计数器,其计数输出端Q3、Q2、Q1、Q0分别与ADS8402的4根地址线相连。计数器上电复位以确保系统从0号通道开始采样。将ADS8402的转换结束信号EOC作为计数器的时钟信号,实现一路转换结束后自动启动对下一路模拟输入的采样控制。

A/D采样过程的控制采用有限状态机来实现,把某一通道的采样过程划分为7个状态,如图2所示。首先S0状态对各个控制信号进行初始化。在S1状态产生ALE信号的上升沿,锁存通道地址。启动信号START应在产生ALE信号的同一时钟下降沿产生,由于VHDL语言在同一进程内不允许时钟的两个沿作为敏感变量,所以将产生START信号单列为一个状态S2,启动转换。在启动转换后,ADS8402使EOC置为低电平,设置S3状态等待A/D转换结束。转换结束后,EOC信号由低电平转换为高电平,状态机进入S4状态,开启输出允许OE。状态机进入S5状态,开启数据锁存信号LOCK锁存数据。为产生与其他进程通信的信号,状态机设置S6作为最后一个状态,然后跳转回SO初始状态。

2.4.2 FIFO读写控制模块

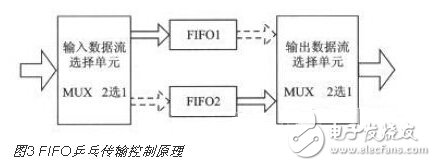

采用2片FIFO轮流读写操作,实现FPGA与PC机之间的数据缓存。乒乓传输控制原理示意图如图3所示,图中的实线箭头与虚线箭头分别代表不同的读写数据周期。输入数据流通过输入数据流选择单元,等时地将数据流分配到FIFO1、FIFO2中。在第1个缓冲周期,将输入的数据流缓存到FIFO1。在第2个缓冲周期,通过输入数据流选择单元的切换,将输入的数据流缓存到FIFO2,与此同时,将FIFO1缓存的第1个周期的数据通过输出数据流选择单元的选择,送到数据流运算处理模块被运算处理。在第3个缓冲周期,通过输入数据流选择单元的再次切换,将输入的数据流缓存到FIFO1,与此同时,将FIFO2缓存的第2个周期的数据通过输出数据流选择单元的切换,送到数据流运算处理模块被运算处理。如此循环,周而复始。

2.4.3 SPC3控制模块

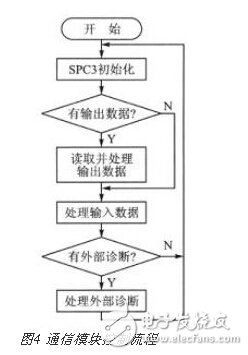

由于SPC3集成了完整的DP协议,因此在进行通信时,FPGA不用参与处理DP状态机。主要任务是根据SPC3产生的中断,将SPC3接收到的数据转存,组织要通过SPC3发给的数据,并根据要求组织外部诊断。在SPC3正常工作之前,需要进行初始化,以配置需要的寄存器,包括设置协议芯片的中断允许,写入从站识别号和地址,设置SPC3方式寄存器,设置诊断缓冲区,配置缓冲区、地址缓冲区、初始化长度,并根据以上初始值得出各个缓冲区的指针和辅助缓冲区的指针。通信模块的控制流程如图4所示。

3 系统的FPGA实现

3.1 Nios II系统架构设计

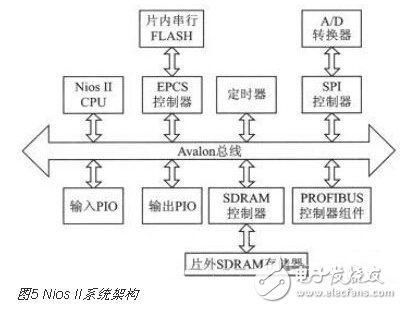

Nios II系统模块包含:Nios II处理器、Avalon总线、并行输入/输出口PIO、串行外围设备接口SPI、定时器Timer、片内存储器EPCS、片外存储器SDRAM、PROFIBUS-DP的客户定制逻辑。由Nios II处理器完成程序控制,主要负责对温度的采集与数据存储操作,并控制PROFIBUS -DP的通信过程。其架构如图5所示。

3.2 系统软件设计

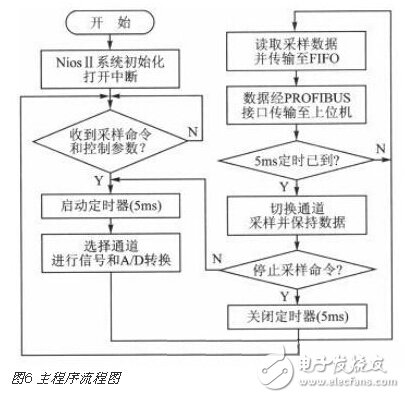

Nios II处理器的软件设计是在软核内存放一段编写的C/C++语言控制程序。来控制系统运行,它可以读写芯片的存储单元,同时与外围的设备进行通信。在本系统中,Nios II程序的任务是:在规定的周期内,FPGA通过通信模块接收上位机发出的采样任务及控制参数,然后控制模拟选择开关ADG706和A/D转换器ADS8402,使它们对选定通道的模拟信号进行调理及A/D转换,并读取采样数据以乒乓传输数据方式传送至片外FIFO缓存,再通过PROFIBUS—DP通信接口将采样数据传输至上位机。主程序流程如图6所示。

结语

基于FPGA的多通道实时温度采集系统以Nios II软核处理器实现SOPC,进一步简化了硬件设计。与传统的基于MCU的多通道温度采集系统相比,该系统具有资源配置灵活、运行稳定

- nRF905实现无线温度采集系统(03-19)

- 基于NRF905的无线温度采集系统的设计方案(02-10)

- 热释人体红外模块温度采集系统电路设计(11-24)

- 温度采集系统电子电路设计攻略(04-27)

- 电池供电超长,无线温度采集器电路和器件选型应该这样来设计(08-05)

- SOPC_SOPC是什么?(02-08)