布线设计时,怎么解决不同电压域的问题?

在同一块芯片上使用不同的电压一直以来都是一个现实存在的问题。

不管你是想将高电压模拟信号和低电压存储混合还是想在同一个数字芯片使用多个VDD,你都需要解决在布线和电路布局上由不同的电压带来的影响。另外,不管你是更关心信号集成还是更关心长期的稳定性,你都要面对一个最基本的问题:在保证不出问题的前提下,这些不同的电压区域之间至少需要相距多远?

过去,解决这一问题的最好方法是在PCB板的顶层进行标记,这样人们就知道那块区域使用的那个电压了。设计和验证也在他们的操作中使用标记层,这种方式看起来似乎还不错。

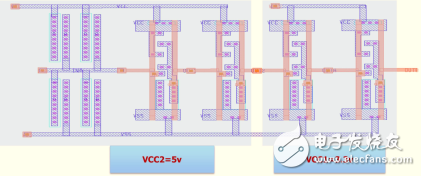

使用标记层区别不同的电压区域

对于只有很少不同电压区域而且每种电压之间的区别比较明显的设计来说,这种方法还算不错。使用这种方法需要设计者清楚地知道每一块区域的范围,并且采用合适的标记层……另外还要保证设计师有足够的时间做这种事,并且不会忘记。

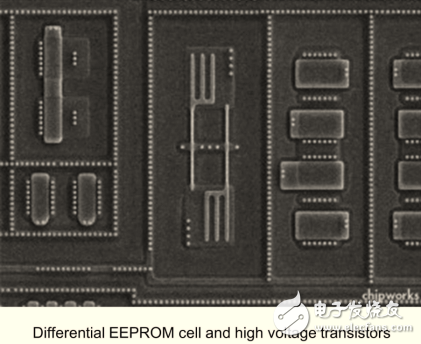

当然,IC设计的世界不会永远那么简单。你会遇到越来越多的电压,越来越多不同的电源域。另外,现在很多设计都对尺寸敏感,为了节省工作面积,有时候还不得不将高电压的线路穿过低电压区域进行走线。这些因素要求更为细腻的精度和控制,这就需要多边形级电压依赖性DRC(设计规则检查)检查方法。这种方法的思路非常简单,和使用标记层标记不同,只需要简单将电压信息放入多边形区域中,验证工具就能根据最大/最小电压的范围计算出最接近的空间布线规则。

多边形级电压依赖性DRC(设计规则检查)检查方法的简单演示

使用这种方法时,DRC工具可以使用实际的最大/最小电压信息来决定要应用怎样的最小间距规则。比如说,如果两条相邻的走线之间的最大可能的电压差为1.5V,然后就采用X规则。如果这一数值是2.1V,又采用另一种规则Y。通过这种检查方法,可以最大化的减少电路所需要的面积,并且又确保了制造工艺上的限制。

这种方法所带来的最明显的挑战是必须要先确认最大和最小电压值,并且要将其注释到布局网中。一旦电压生成,就需要将其标记到布局中。但是布局工程师可不想在录入这样的信息上浪费时间。那有什么方法可以自动完成吗?

生成最大/最小电压的方法依赖于设计流程,对于模拟设计来说,SPICE仿真是已经完备的并且能覆盖每个节点的整个动态范围,所以可以直接从已有的仿真流中导出每个区域的最大/最小电压值。而对于数字设计来说,难度就大得多了。

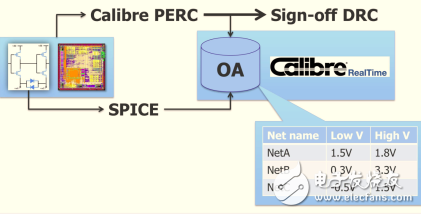

对于数字设计,我们建议使用自动化工具从引脚向内部网络传递电压。这些工具应该能将每个引脚的电压都传递到内部节点上,然后再为每一个内部网络提供完整的动态范围。然后该工具就可以自动地将最大/最小电压标记在每张布局上并签核DRC。

用于签核和互动修复的电压依赖性DRC流程。Calibre PERC和Calibre nmDRC的结合为你提供了一个完整的流程,以在采用的布局上生成所需要的电压信息,并根据工厂的DRC签核要求进行验证。

来自这种流程的错误会在设计环境中高亮显示,其它的验证错误也会如此。但是,其结果只会包含错误本身的信息(电压差和相关的错误);为了消除这个错误,布局工程师需要更多的了解这个错误。比如说,如果有一个涉及到两个区域的错误,两者之间的电压差为2.2V,那么这时应该选用的间隔是X……但是这些电压差从何而来?那块区域拥有怎样的电压值?该信息出现在验证流程中,而不是出现在设计环境或结果之中。

幸运的是,你可以以某种格式导出电压和布线网络的信息,并将其导入到OpenAccess数据库中作为一系列的限制信息。你应该使用一种能够识别这种信息的工具,并将其提供给用户交互,并将这些电压信息添加到多边形中进行交互认证。

通过将合适的自动化工具和自定义设计环境进行结合,可以提供一个集实现、优化和验证电压依赖性布局的完整系统,从而得到更小、更高效的布局,并最终为多电压域项目的研发节省了时间和资金。

- Protel软件在电路设计中的应用(02-28)

- PCB布线技术中的抗干扰设计(03-08)

- 浅谈开关电源设计中PCB板的设计注意事项(07-08)

- 新应用指南部署光纤基础设施结构化布线(04-15)

- 综合布线、报警、消防通信系统三者的联系(11-25)

- 通信网络综合布线的注意事项(02-19)