基于ARM和FPGA的嵌入式数控系统设计

的控制。

4 基于FPGA的DDA精插补器设计

随着FPGA器件及其开发技术的日臻成熟,采用FPGA实现运动控制的方案显示出巨大的潜力。由于FPGA的设计是并行的、多线程,而且具有在线可编程能力,兼备了速度快和成本低的优点,同时克服了专用处理器灵活性方面的不足。基于FPGA的DDA精插补器相对传统的软件插补具有强大的优势。

4.1 数字积分插补算法

目前比较成熟的数控插补算法有逐点比较法、最小偏差法和数字积分法等,数字积分法又称数字微分分析器(Digital Differential Analyzer,DDA)。采用该方法进行插补,具有运算速度快、逻辑功能强、脉冲分配均匀等特点,可实现一次、二次甚至高次曲线插补,易于实现多轴联动。

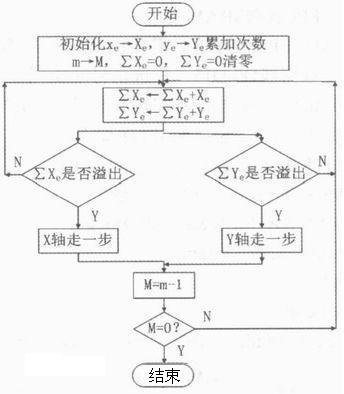

数字积分插补算法是将函数的积分运算转换成变量的求和运算。如果所选择的脉冲当量足够小,则用求和运算代替积分所引起的误差可以不超过允许的数值。采用两个寄存器(函数寄存器和累加寄存器)和一个全加器构成数字积分器,将单位周期选得足够小,每单位周期都向累加器累加函数寄存器中的数值,如果累加器溢出,就向外发送脉冲,实时地改变函数寄存器的值,就可以完成步进电机的调速。DDA插补控制器设计的硬件描述语言程序的流程图如图3所示。

图3 DDA插补控制器设计的硬件描述语言程序的流程图

4.2 数字积分插补的FPGA实现

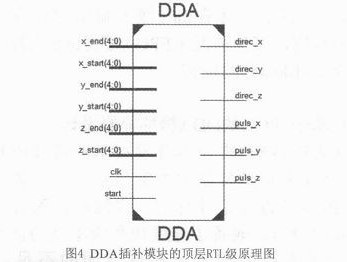

采用有限状态机的设计方法,每个轴的数字积分插补均由一个三状态机的积分累加器完成。本系统的FPGA开发环境为Xilinx公司的 Xil inx ISE,并结合ModelSim仿真软件对整个系统进行了全面的功能验证。如图4所示为DDA插补模块的顶层RTL级原理图,由图5可知DDA插补模块的输入信号为各轴的起始坐标以及时钟信号和启动信号,输出信号为各轴的脉冲信号和方向信号。

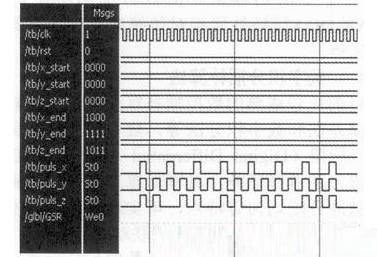

图5 DDA插补模块仿真波形

运用ModelSim仿真软件对DDA插补模块进行仿真验证。测试数据的起点坐标为(0,0,0)终点坐标为(8,15,11),仿真结果如图5所示,显示系统很好的完成了三轴的脉冲分配。

4.3 加减速控制模块

加减速控制是数控系统的关键技术之一,也是实现数控系统高实时性的瓶颈。数控系统中,为了保证机床在启动或停止时不产生冲击、失步、超程或振荡,必须对进给电机的脉冲频率或电压进行加减速控制。即当机床加速启动时,保证加在电机上的脉冲频率逐渐增加;而当机床减速停止时,保证加在电机上的脉冲频率逐渐减小。目前,电机加减速的常用控制方法是梯形加减速控制和S形加减速控制。本次设计采用两种控制方案以适应不同工作场合的要求。

4.3.1 梯形加减速

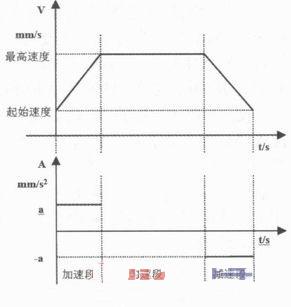

梯形加减速是指在加减速过程中加速度为常数,速度曲线为梯形的加减速过程。梯形加减速控制算法简单、易于实现,但在加减速过程中加速度曲线不连续会导致驱动机构的振动和冲击。正常情况下梯形加减速运动过程如图6所示分为加速段、匀速段和减速段三个阶段。

图6 正常情况下梯形加减速运动过程

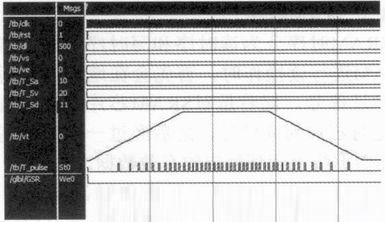

图7所示为ModelSim对梯形加减速模块的仿真结果,可以看到插补器输出的脉冲速度曲线呈现梯形,输出脉冲的频率的大小随速度的变化而变化,实现了电机的梯形调速。

图7 ModelSim对梯形加减速模块的仿真结果

4.3.2 S形加减速

S形加减速是指在加减速时,加速度导数为常数,速度曲线为S形曲线的加减速过程。通过控制加速度导数来避免加速度突变,减小加工过程中由于加速度突变引起的机械系统振动。S形曲线速度控制可以得到平滑的速度曲线,但算法复杂,运算时间长。

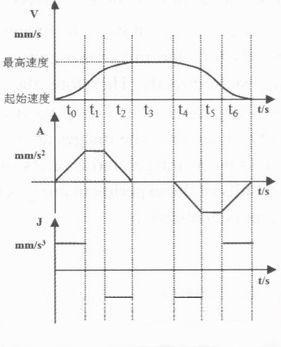

图8 S形加减速曲线图

S形加减速中加速度相对加速度导数的变化规律相当于直线加减速中速度相对加速度的变化规律。如图8所示为S形曲线加减速的曲线图,图中从上到下依次为速度曲线、加速度曲线以及减速度曲线。从图中可以看出,正常情况下S形加减速分为:加加速段、匀加速段、减加速段、匀速段、加减速段、匀减速段和减减速段七个阶段。加速度连续,调速光滑,不会导致驱动机构的振动和冲击。

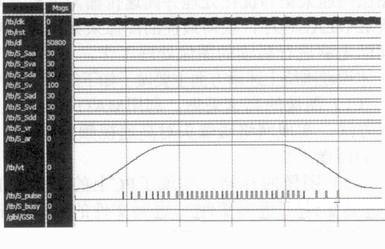

图9 ModelSim对S形加减速模块的仿真结果

图9所示为ModelSim对S形加减速模块的仿真结果,可以看到插补器输出的脉冲速度曲线呈现梯形,输出脉冲的频率的大小随速度的变化而变化,实现了电机的S形调速。

5 结束语

本文给出了一种基于ARM和FPGA的开放性的嵌入式数控系统,突破了传统的计算机数控系统架构,采用ARM处理器S3C2440A和 FPGA器件XC3S25 0E和μC/OS-II嵌入式实时操作系统组成的数控系统软硬件平台,充分利用了ARM微处理器的高速运算能力与FPGA的快速配置能

- 基于高档数控系统的实时多任务实现(09-27)

- 机床数控系统中嵌入式plc的设计(02-06)

- 基于线程局部存储技术的多通道数控系统仿真(11-13)

- 嵌入式系统在电源设计中的运用(09-20)

- 一种小型智能化UPS系统的嵌入式设计方案(09-16)

- 基于无线传感器网络的嵌入式远程测控系统研究(10-17)