意法爱立信移动平台多核处理技术

在软件方面,如果把架构的全部潜力都发挥出来,系统异质管理对于操作系统可能是一件非常复杂的任务。理论上,操作系统应该有足够高的智能,能够区别要求条件不同的应用任务,将其分配给大处理器或小处理器执行。为限制在昂贵的集群器间移植软件,这些决策应该相对稳定。同时,应用软件可能会突然改变行为,系统必须能够迅速做出响应,这需要提高动态电压和频率,而且在两个集群器上单独进行,增加要考虑的功率状态的数量。不仅今天的操作系统无法提供发挥多核处理器的全部潜能所需的先进复杂技术,而且错误的决策在实际应用中可能会适得其反,大量的软件移植会引起用户可见的系统故障,错误决策引起性能降低或浪费电能。

完美地支持异构多核处理器需要多年的研发活动和优调技术。

为了限制系统做出错误决策的风险,研发人员开发出了中间解决方案,但是,该解决办法需要以降低多核处理器潜能利用率为代价。例如,某个解决方案通过专属方式使用大小 集群器,即不是并行处理,而是根据系统总体负荷从一个集群器切换至另一个集群器,以避免智能映射每个独立软件线程变得更加复杂,这种方法的缺点是没有并行使用集群器,所以没有发挥多核处理器的全部潜能。

另一个最新的方法是把大小处理器整合成一对固定的处理器,操作系统负责管理每个大小处理器,将其视为一个电压/频率工作点扩展的单一抽象处理器,这种方法的缺点是在集群器之间频繁移植软件具有一定的风险,抽象处理器的工作模式配对不是原生的,因为在硬件上,工作点是由集群器实现的,而非大小处理器对。

总之,异构多核处理器当然是一项前景不错的技术,特别是在移动市场。然而,因为技术复杂,特别是在软件方面,这项技术需要经过多年的研发和优调才会发挥出全部的潜能。

硅制造工艺的新进展: FD-SOI

近些年,为确保硅制造技术节点进一步降低,突破传统技术即将达到的极限,半导体企业进行了大量新技术研发,取得了很多具有突破性的开发成果,例如, FinFET 和 FD-SOI 制造工艺。

意法·爱立信将意法半导体的FD-SOI (全耗尽型绝缘体上硅)技术用于其性能非常优异的下一代28nm 移动平台。在这里,我们只从计算性能的角度简要分析FD-SOI 的技术优势,说明此项技术如何能够进一步提升单核处理器的性能,让我们继续专注速度更快的双核处理器,以获得更高的软件性能。

如图7 所示,由于插入超溥埋氧层衬底,FD-SOI 使晶体管电特性得到大幅提升,同时继续使用非常成熟的平面工艺制造芯片。

下面概括FD-SOI 的优点

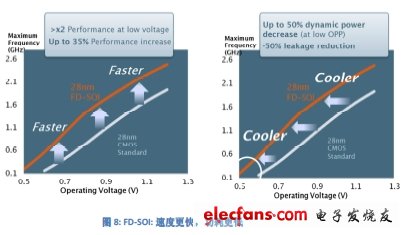

· 速度更快:在相同的技术节点,FD-SOI 晶体管的沟道比体效应晶体管的沟道短,而且前者是全耗尽型沟道,无掺杂剂。在这两个因素共同作用下,FD-SOI 晶体管在相同电压时开关速度更快,在功耗相同条件下,高压工作频率提高35%,低压工作频率提高。

· 功耗更低:有多个因素促使功耗降低:全耗尽沟道消除了漏极引起的寄生效应,在低功耗模式,可更好地限制载流子从源极流向漏极;更厚的栅电介质层可降低栅极泄漏电流;更好地控制体偏压技术 (为更好地控制速度和功耗而向晶体管体施加的电压)。结果,在高性能时,功耗降低 35%;在低性能时,功耗降幅更大,高达50% 。

· 工艺更简单:FD-SOI 制造工艺与28nm 体效应技术(bulk)的相近程度达到 90%,总工序减少15%,研发周期更短。此外,FD-SOI 技术无需压力源或其它类似的复杂技术,而其它工艺可能需要这些技术。最终工艺的复杂度低于体效应技术,远远低于技术。

从微处理器设计角度看, 相对于体效应技术,FD-SOI 的优势十分明显(见图

· 电压/功耗相同时,FD-SOI 可取得更高的频率,或者在频率相同时,FD-SOI 的功耗更低;

· 可取得的最高频率更高

· 采用FD-SOI 技术的处理器能够以更低的电压维持非常不错的频率 (比如,1GHz,0.65V),在低功耗模式时, FD-SOI 的对比优势更加突出,如图8 的低压区所示,在低功耗模式,的频率比bulk 技术高100%。

在高频率时,能效提高幅度大约35%。在大量的用例中,这个成绩足以让FD-SOI 双核处理器战胜速度较慢的bulk 四核处理器,如前文所述,这是因为目前软件性能提升受限。

在低功耗方面,FD-SOI 技术的影响更大,无需采用更复杂且还不成熟的异构多核处理器降低功耗的方式。

上文论述的扩展的工作模式是以前提到的FD-SOI 的技术优势共同实现的,其中体偏压(body biasing)扮演重要作用。体偏压是在晶体管体上施加

- 半导体制程到了十字路口 对物联网应用是好消息(07-31)

- 格芯发布基于领先的FDX? FD-SOI技术平台的毫米波和射频/模拟解决方案(08-27)

- 格芯CEO:FD-SOI是中国需要的技术(08-29)

- 多核处理器在汽车电子中的应用(02-07)

- 面向多核DSP及SoC的平台软件解决方案(05-14)

- 专家点津:多核处理器将如何改变电源管理?(11-16)