PCB布线产生的寄生电感对DC-DC效率的影响

换频率≥600kHz时。

漏极电感的影响

漏极电感会引起严重的振铃,可能足以导致MOSFET在极限条件下击穿 (图3)。它亦对效率有不利影响。

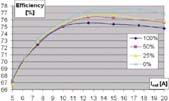

图6所示效率是指不同频率下负载电流和漏极电感的函数。此外,可观察到如下结果:

当电流为15A时,在300kHz和50%电感条件下我们就不得不中止试验,因为MOSFET的温度超过130℃。在同样频率,100%电感的条件下,我们无法得到任何读数,因为振铃太过严重。

在300kHz、12A条件下,漏极电感的50%比0%的效率将减少7%。由于MOSFET温度过高,15A以上便无法进行试验。

在600kHz,12.5A条件下,漏极电感的50%比0%的效率将减少8.5%。由于MOSFET温度过高,12.5A以上便无法进行试验。

在1MHz时,由于MOSFET温度过高,5A以上便无法进行试验。

栅-源极电感的影响

较大的源极电感会使效率明显减小 (见图5和图7)。

前面(见图4)已显示出效率对栅极电感的基本依赖关系。当结合小源极电感时,其整体状况就相当清楚——较大的栅极电感必然造成较大的功率损耗。为了理解图7所示的关系,我们进行了仿真 (见图8)。

该结果的解释需要进一步研究。现在我们可以说明,在电路板合理的电感值范围内,漏极和源极电感必须减小,以确保高的转换器效率。该仿真得出如下结果:

栅极和源极电感与MOSFET的栅源电容产生共振。HS-FET关断栅-源时,电容通过这些电感路径放电。MOSFET关断后,电感将迫使栅极电流继续流动并对栅-源电容进行反向充电。该充电将再次以相同方式放电并使HS-FET的栅-源电压反向。根据减幅的情况,HS-FET可再次导通并出现巨大的短路现象。在如此高的栅极电感下,该影响变得严重。在某些情况下,甚至可以见到第二短路影响。作为这一共振电路的部分,源极电感还可以第二种方式发生作用。当发生短路电流时,源电感可限制短路电流的di/dt (电流随时间的变化率),从而限制损耗。源极电感还会对栅源电压造成负反馈,并限制短路。在寄生栅极电感高的情况下,尤其会发生这些影响。为了获得高效率,应该通过设计避免这种影响,即必须仔细设计将栅极电感降至最小。

源极 HS - 源极LS电感的影响

我们研究了寄生源极电感的位置对效率的影响。结果在相同数值的寄生源极电感回路中,控制FET将比同步FET对其效率的影响更大 (见图9)。

这种现象的原因在于慢速开关控制FET引起了额外的开关损耗,因为在变换过程中控制FET的VDS较同步FET高 (同步FET的正向电压降小)。此外,寄生电感对FET栅-漏电压的反馈对总体HS-FET漏电流造成重要影响。通过比较,寄生源极电感对LS-FET漏电流的影响只是局部,这是因为可通过同步FET的体二极管对其进行旁路。

并联MOSFET的影响

当MOSFET并联时,很多情况下每个单独的MOSFET回路不可能具有相同的寄生现象。我们已经研究了MOSFET漏极回路中的额外电感对于效率的影响。

从(见图10)中,我们观察到寄生电感的差异越大,效率下降得越大。引出的问题是:"如何优化设计?"换句话说,使两个MOSFET具有相同大的寄生电感,是否比保持原状好?

结论

我们通过试验显示寄生电感对于DC-DC转换器中开关MOSFET效率的有害影响。 结论如下:

源极电路中电感的影响最为严重,其次是漏极电路中的类似电感。

在我们的试验板中,我们没有发现与栅极电路电感相关的严重影响。

效率的降低与转换器的切换频率有密切关系。

效率的降低与负载电流有很大关系。在源极和漏极电路存在寄生电感的情况下,负载电流越大,效率下降越多。

在现今DC-DC转换器应用中,进行功率系统PCB布线时要特别小心,在开关MOSFET周围尤需注意。

使用多层板的优点之一便是通过汇集尽可能多的层板中的电流,减小寄生电阻和电感。这样可降低电阻损耗和寄生电感造成的损耗。

在设计高频DC-DC转换器时,存在许多与源极和漏极电路相关的寄生电感问题。首先是封装电感,可行的做法是使用新近推出的低电感封装,用于封装开关MOSFET。第二项是PCB寄生电感,必须使用多层PCB并使迹线电感降至最小,以控制损耗。这样设计人员便可以使用较少的几个电容获得更快速的动态响应,并成功实现高频设计。

应该将无法通过设计来避免的寄生电感移至同步FET回路中,因为同步FET中的电感对于总体效率的影响比控制FET回路中电感的影响小。备注:在低占空比的情况下,同步FET回路中的寄生电阻会显着降低效率。需要在设计 (迹线宽度、铜层厚度、有效的回路范围、偏置等) 中作出复杂的折中平衡。

最好避

- 为EMI敏感和高速SERDES系统供电(08-17)

- 高可靠DC/DC变换器模块设计(09-15)

- DC/DC转换器的发热问题缘由(10-30)

- 一种CMOS绿色模式AC/DC控制器振荡器电路(09-16)

- 凌力尔特大功率多相同步升压型DC/DC控制器LTC3787(10-15)

- 电动 / 混合电动汽车电池管理系统的可靠性(11-09)