基于莱迪思FPGA的DVI/HDMI接口功能的设计和实现

列是集成了SERDES的低功耗、低成本FPGA,拥有很宽的温度范围。这些器件具有高达16个通道的SERDES,可处理 250Mbps~3.125Gbs的数据速率,且无过采样情况。DVI/HDMI是ECP2M和ECP3系列支持的模式之一,能够实现这个设计是因为莱迪思已对T M D S信号传输构建了一个独特的接口。在DVI/HDMI电缆中, T M D S信号是有一个外部时钟的源同步信号。莱迪思已开发出一种技术,利用ECP2M或ECP3中内置的SERDES恢复并产生针对T M D S的合适的数据和格式。这种实现是可能的,因为内置的SERDES有250Mb/s到3.2Gbp/s的宽动态范围。

莱迪思的DVI/HDMI参考设计集成了发送和接收功能,使得用单芯片解决方案能够实现一些有趣的应用程序。例如,可以针对设计使用传输方向,从原来的7:1 LVDS显示驱动器转换至DVI。在接收端,用接收到的HDMI数据实现一个HDMI扩展器,然后将它格式化并通过另一种接口(如光纤或CAT5)送出。另一种应用是HD-SDI到DVI的转换,或反之亦然。针对图形叠加、画中画和分屏应用,HDCP协议的许可证可以进一步处理和管理音频和视频数据流。

基于ECP2M的接收功能实现

DVI/HDMI参考设计有发送和接收功能。在接收端,ECP2M利用内置模块 SERDES恢复T M D S信号,通过SERDES内的时钟和数据恢复(CDR)电路完成这个处理。CDR电路将每个串行的T M D S通道转换至10位,并将具有同步时钟的数据传送至FPGA接口,然后在FPGA中进行数据处理达到同步。这要求有三个级别的同步,分别是在本文中称为 "字节对齐"的10位同步、通道调整、多通道对齐。文章的后面讨论这些步骤。接下来是自动检测正在运行的数据流的分辨率(480p、720p、1080p 或1080i),并调整物理编码子层(PCS)参数。当在这些分辨率之间动态切换时,应保证优化运行。针对发送端,没有必要进行字节和通道对齐。10位模式的PCS是用来使数据串行化,并与液晶显示屏通信。

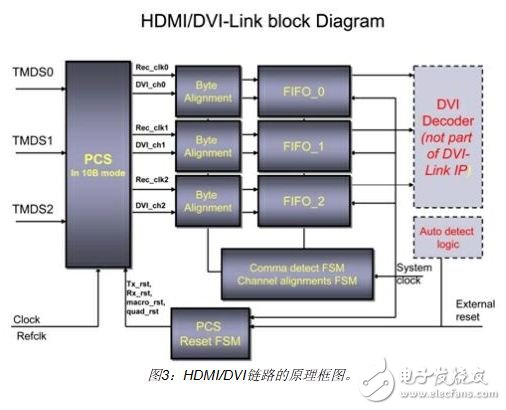

ECP2M/ECP3 的CML SERDES输入(见图3的接收信号流)收到T M D S三个通道的信号(0、1,和2)数据。由于DVI/HDMI的信号不采用标准的8B/10B编码,SERDES后面的PCS设置成10位模式(旁路)。 T M D S信号传输使用对本协议唯一的四个对齐的字符(不同于8B/10B方式)。串行器与SERDES的CDR传递10位的原始数据,FPGA进行字节对齐。 DVI/HDMI链路连接能以多个不同的频率发送数据,自动检测逻辑被用来检测正在传送的是哪种分辨率,并配置PCS以便在SERDES锁相环中实现锁定。

接收同步

一旦10位数据在FGPA中,执行上述定义的三个步骤(字节对齐、通道对齐、多通道对齐)是必须的 。字节对齐:设计确定在数据流的哪里是10位数据字节的开始和结束。在FPGA结构中使用有限状态机(FSM)来完成这一任务。把数据流的第一个和第二个 10位组合在一起,形成一个20位的总线;然后分解至9位、10位总线。在这一阶段,数据与对齐的字符进行比较,当字符顺序发生了8次(称为单通道对齐),同步信号有效。状态图如图4所示。

同步检测之后,对齐数据的字节写入FIFO。当所有三个通道都完成了"通道对齐",就可以写入FIFO,至此通道对齐的任务就结束了。在这一阶段, FPGA将等待直到FIFO处于半满状态,并在同一时间(多通道对齐)对三个FIFO进行读操作 。这将保证三个通道对齐,并同步。

基于ECP2M的发送功能实现

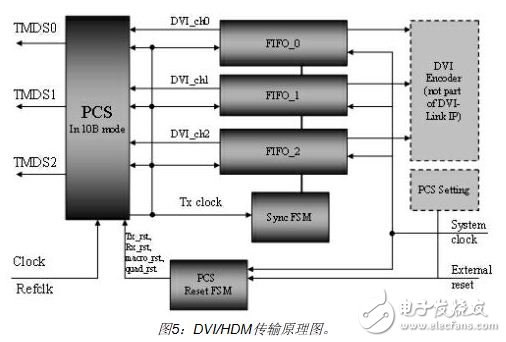

ECP2M传送锁相环有最佳的操作范围,预定义的范围为:Low、MedLow、 Med、MedHigh 和 High。通过SCI总线,所有这些范围在ECP2M中都是动态配置的。因为有各种各样的显示分辨率,针对理想的输出率,DVI/HDMI参考设计必须有 SERDES组。例如,如果要求一个720p的HDMI显示,即742.5Mbps,SERDES PCS必须设置在适当的范围(MedLow)。显示的数据是放置在一个由DVI/HDMI参考设计定义的FIFO中。同步从三个T M D S的每个通道中读取数据,然后将FIFO的数据移至PCS,再用SERDES进行传输。PCS设置成10位模式,串行输出FIFO的数据。在这一阶段,采用合适的时钟,数据将被转换为新的T M D S 流,使接收器恢复信号,如果配上显示器,就会出现图像。具体原理见图5。

系统演示和验证

这个DVI/HDMI参考设计是经过检验和验证的,并遵守相关规范。莱迪思已经实现了DVI环回演示,展示了设计的功能。可用ECP2M50E-SEV SERDES评估板和其它硬件来进行演示,莱迪思半导体公司提供评估板和其他硬件。除了电路板之外,系统演示还需要DVI至SMA的接口卡、各种DVI和 SMA电缆、一个DVI源和监视器。整个演示和测试设置如图6所示。

通过DVI至DVI或HDMI

- 莱迪思将展出低成本图像传感器桥接参考设计(11-13)

- 莱迪思技术专家分享:基于FPGA的视频监控时代(02-21)

- 基于莱迪思FPGA的视频显示接口的实现(03-28)

- 莱迪思iCEstick评估套件以低成本和低功耗加速FPGA设计(07-29)

- 莱迪思MachXO3 FPGA系列 助力新兴互连接口设计(09-09)

- 莱迪思CrossLink 视频接口桥接方案(09-19)