用EPLD实现单脉冲二次雷达的应答解码处理

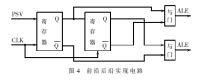

单脉冲二次雷达的PSV信号是由接收机和通道(∑)内的应答信号,经过特定门限电平进行二值化处理后输出的0或1电平。前后沿的提取,可以将PSV信号输入两个寄存器,通过与门电路实现。实现电路如图4所示。

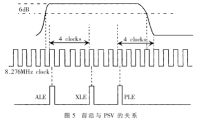

ALE与ATE分别是与时钟脉宽(0.1208μs)相同的前沿与后沿。当PSV信号的宽度大于一个应答码的宽度时,就认为接收到的是两个或多个脉冲的混叠,于是产生了一个伪前沿(PLE)。PLE的产生时间是从ATE开始向前数四个时钟周期(因为一个标准的脉冲宽度为四个时钟周期),如果PSV的脉宽更长,可认为有更多个应答脉冲的交叠,一个额外前沿(XLE)在ALE与PLE之间产生,在以后的处理中只用于帮助判断结果的正确性。前沿与PSV的关系如图5所示。

3.2 视频采样

视频采样分为ALE采样与PLE采样。

ALE采样使用了4×4寄存器阵列,这样就能够存储多于一个的采样值。为确保寄存器阵列的建立与保持时间,ALE脉冲经一级触发后,由延迟器产生一个40μs的延迟,并限制写脉冲到30μs。寄存器阵列的写地址由4位计数器产生,每个采样脉冲计数器加1。PLE采样与ALE采样电路不同之处是它只需要存储一个PLE采样值。本系统的采样时钟为8.276MHz。

3.3 SDR计算

由于SDR模块中采用了对数运算,所以在进行和幅度与差幅度比值的运算时,只需要将差信号反相后接在加法器的输入端。除在波束中心外的和信号小于差信号外,△-∑在波束中心出现负峰值,所以在负峰值最大处为波束的中心。根据其他△-∑的值并参照负峰值,可转化为偏离波束中心的角度。

3.4 框架检测与应答解码

正常情况下,两个框架脉冲的间隔为20.3±0.1μs,因此,一个框架就认为两个前沿间有167、168或169个时钟周期。本系统框架脉冲的检测是根据比较延时的前沿与非延时情况下的重合情况,如图6所示。延时的前沿对应于框架脉冲F1,非延时的前沿对应脉冲F2,F1相对于F2延时20.3μs。由于F2相对于F1有3个时钟脉冲的变化范围,所以F2与F1的前沿延时167、168或169个时钟周期的任一个对齐,都认为是一个正确的框架。

以下三种情况下框架检测将被禁止:

(1)F1、F2都是来自旁瓣的应答信号;

(2)两个相邻的框架之间的间隔小于3个时钟周期;

(3)S模式的头应答被检测到,框架检测间被禁止120μs,因为一个S模式应答持续120μs。

应答信息相互交织产生幻影框架,如图7所示。假如只用框架脉冲间的时间间隔为20.3μs的原则检测,可检测到4个框架脉冲对,框架检测器不能区分"虚假"框架和来自飞机的真实框架脉冲对。

补救措施是同时只处理两个应答。当第一个应答被检测到,随后21μs中检测到的应答为临时应答,如果另外又发现一个重叠应答,这个临时应答就被取消此过程重复进行,直到检测到最后一个应答,此应答被保留。因为第一个检测到的框架肯定是真实应答,没有更早的脉冲产生错误框架。同样,最后一个框架肯定是真实应答,没有更晚的脉冲能产生错误框架,中间检测到的框架是可疑的,假定它们不正确。

当一个正确的框架被检测到,接下来的任务就是检测此次应答码的内容。首先,解码过程依据每个应答码间的时间间隔都是1.45μs,SPI与F2间的时间间隔是4.35μs,因此在离框架脉冲各个应答码可能出现的位置上检测是否有应答脉冲出现。考虑到每个应答码与框架脉冲间的时间间距有一定的允许误差,在距框架脉冲相应的应答码出现的位置上,提前或延后一个时钟周期都认为是正确应答码的位置。将相对于框架脉冲可能出现应答码的位置上的值与框架脉冲(非旁瓣脉冲)比较,得出应答码为1或0,有以下几种情况:

(1)高置信度0:在应答码出现的地方没有检测到应答脉冲的存在,若仅以幅度测量,则仅出现低幅度值。

(2)高置信度1:在应答码出现的地方出现主波束内的应答码,幅度与其对应的参考脉冲相关,与其他应答的参考脉冲不相关。

(3)低置信度0:若此应答脉冲被标记为旁瓣应答脉冲或此应答脉冲与相应的参考脉冲不相关,则与其他应答的参考脉冲相关。

(4)低置信度1:主波束应答码存在,但与参考脉冲不相关或与另外应答的参考脉冲相关,或既与相应的应答框架相关又与另外的框架相关。

3.5 码装配

码装配包括SVA代码装配器和SDR代码装配器两部分。SVA代码装配器的功能根据SVA平均值进行置信度确定,产生对应的置信度码位;SDR代码装配器的功能是检测到一个框架对 F1、F2时,便检查该应答脉冲的内容。对每个代码位,根据SDR 平均值进行置信度确定,产生对应的置信度码位,然后将该代码和置信度位与来自SVA装配器的相应位进行组合。

因为最多能同时处理四个

- 航管二次雷达射频切换单元FPGA实现(03-01)