基于DRFM的欺骗干扰与雷达目标模拟实现

时间:07-06

来源:电子工程师/作者:罗进

点击:

引言

在雷达的测试系统中,常常需要模拟日标回波;同时,为了测试雷达的抗干扰特性,还需要产生欺骗干扰的信号。DRFM|0">DRFM(数字射频存储器)由于可以高保真的存储和复制采样信号,测试系统不仅可以产生多个假目标,还可以产生距离拖引干扰和速度拖引干扰。

1 系统组成及原理

雷达的测试系统需要模拟目标的航迹。对于高速运动的目标,其控制系统需实时计算控制参数,供功能块使用。因DSP(数字信号处理器)芯片采用的是哈佛结构的并行体系结构,具有独立的数据存储空间和程序存储空间,它的数据和程序分别存储在不同的存储器之中。采用TI公司的DSP处理芯片,其中TMS320C2000系列是面向控制型的处理芯片,也有较强的计算能力,以适应快速数字信号处理运算的要求,比较适合本系统使用,可以实时计算下载控制参数,供功能块使用。

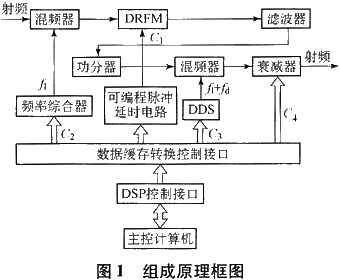

测试系统包括以下几部分:

a) 系统通过天线接受雷达信号,经混频成中频后,通过DRFM采集中频雷达脉冲信号,并把采集数据存储在存储器中供读取。

b) DSP根据主控计算机提供的命令和干扰参数,实时计算每一个更新时刻计算出相应的目标时延和多谱勒频移,并把数据 存入相应的锁存器中。

c) 可编程脉冲延时电路根据DSP提供的参数,对雷达视频脉冲进行相应的延时,产生DRFM的数据释放信号,控制DRFM的D/A转换器工作,产生中频脉冲信号,从而实现距离拖引干扰。

d) DDS(直接数字频率合成器)模块根据DSP提供的参数,产生相应的多普勒频移信号,经混频电路处理后,实现速度拖引干扰或目标速度模拟。

e) 根据假目标的运动轨迹,DSP实时计算出假目标的距离引起的功率衰减,控制输出电调衰减器,实现假目标的距离欺骗。

目标模拟与欺骗干扰系统组成框图如图1所示。

|

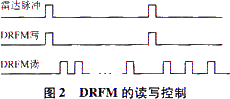

DRFM读取时延的数据更新并不需要每个雷达脉冲都更新,这是由目标的运动速度决定的,一般2 ms更新一次就够了。

可编程延迟电路的延时时间由DSP控制,以接收到的雷达视频脉冲为起始点,计算延时参数,延时脉冲的个数也是可控的,这样可以控制产生多个假目标或多个欺骗干扰信号。

因DRFM可以反复复制存储的信号,可以用一路来实现多个模拟目标或欺骗干扰,为了设计的灵活性,用FPGA(现场可编程门阵列)设计一个有使能端的可设置延时时间和脉冲个数的脉冲延时电路,可以在FPGA中根据需要设计多个单脉冲延时电路,然后将这些脉冲相加,得到延时独立设置的脉冲,模拟独立运动的目标轨迹。这样,只用一个通道就可以同时实现目标模拟与欺骗干扰、多目标模拟或多个欺骗干扰信号。对DRFM的控制时序见图2。

|

当一个通道只有一个目标需要模拟时,只需要将计算好的多普勒频移参数送入锁存器即可。但常常需要模拟多个目标或需要模拟一个目标及与它相应的欺骗干扰,这时采取每计算一个参数送入锁存器的方法来控制就可能来不及了。DSP计算好需要模拟的多个目标的距离和多普勒频移后,将多普勒频移参数按模拟目标相对雷达信号距离由近到远的次序存入RAM中,由于DDS从置数到工作稳定需要时间,以雷达同步脉冲来送出第1个控制参数,其他的在每个脉冲的后沿来更新参数。对于频率捷变雷达来说,多普勒频移与频率相关,如采取测量到雷达频率再计算的方式,当模拟的目标与测试系统较近时,实时更新时间来不及,由于目标运动的速度不快,参数更新时间,采取预先计算多普勒频移并下载到存储器中,以频率做存储器读出时的地址,频率捷变时可以实时查表得到该时刻该频率的多普勒频移。电路原理见图3。在模拟距离远近的功率变化时控制电路与此相似,因与频率无关,电路比控制多普勒频移的电路简单,不再详述。

|

通过一个通道来实现多个模拟目标或欺骗干扰,将减少设备量,降低系统的成本,但当两个目标距离较近、速度不同时,以及模拟目标数较多时,一个通道将难以实现。这时可以通过增加通道来实现。由于与主控计算机是通过串口通信,这样,带来了一个问题,即如何简单实现两个通道间的信号同步。

下面以两个通道(一个通道用做模拟目标,另一个通道用做相应的欺骗干扰)为例介绍通道问同步的实现。将模拟目标的运动参数下载到主模拟通道,而作欺骗干扰的通道,计算机需要将目标参数和干扰参数一起下载,DSP计算时,以接收到的雷达视频脉冲为参考值,计算出干扰更新时刻的距离和速度。由于这样起始点的时刻未知,每个DSP独自更新,将难以保证欺骗干扰和模拟目标时间的一致性,可以采取以主通道DSP为主,更新数据时发出中断信号,另一个接收到更新中断后更新数据,为了保证各数据更新的同时性,采取两次锁存,接收到的雷达视频脉冲产生同步脉冲对数据进行锁存。程序流程如图4所示。

- ISL5216在中频通用接收平台中的应用(05-05)

- MIMO 系统的快速原型设计与验证(04-28)

- 一种基于ADSP-BF537的无线视频传输方案(05-28)

- DSP与普通MCU的区别(08-07)

- ARM、DSP、FPGA的技术特点和区别(01-22)

- 采用DSPBuilder的FIR滤波器的方案实现(02-10)