智能视频监控技术应用及解决方案集锦

µC/OSII是Blackfin所支持的RTOS之一,在高速的Blackfin处理器上有很强的硬实时性能,OS中断响应时间约为110 cycles(600MHz下约0.18us)。系统首先创建一个主任务(main task),负责系统的初始化和创建其他的模块任务。各模块任务独立运行,处理自己的输入和输出数据流,模块之间的耦合程度较低,可以灵活的取舍。网络协 议栈方面,Blackfin上也有多种选择,除了各商业RTOS配套提供的TCP/IP协议栈外,LWIP作为开源网络协议栈中的佼佼者,也在 Blackfin处理器上有移植版本。本项目采用了uC/OSII配套的uC/IP协议栈。

软件架构分为音视频采集,智能分析,编码打 包和网络传输,系统控制等模块,每个模块由不同优先级的任务负责,这非常有利于系统的集成和模块化设计。模块之间相互独立,用信号量进行同步,模块之间的 数据结构都设计成双缓冲或者多缓冲,,保证IO模块和运算模块并行执行。对于高系统负荷下的容错,程序和数据结构也考虑在内,偶然出现的丢帧现象不会影响 系统的继续运行,并且向系统控制部分报告错误。

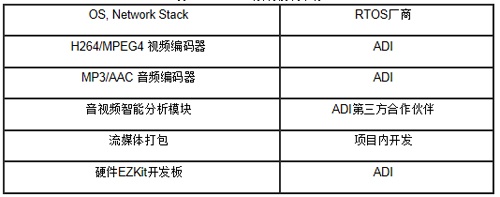

下表(表1)列出了系统中各模块的来源:

表1 IP Camera系统模块来源

3.系统优化

在DSP系统中,一旦算法确定下来,实现过程中的优化思路一般也是固定的,首先利用编译器的一些优化开关和手段,其次对算法做分析,找出关键代码和数 据,对关键部分做一些手工的调整,如改写成汇编等。但在实现一个包括多路输入输出,多种算法并行的完整的系统时,如何达到整体运行的最优化,除了传统的算 法优化外,还需要从系统的角度考虑一些因素:

1.系统带宽的最大化和最优化

在这样的一个复杂系统中,视频和音频数 据 的多路输入输出带来了冲突和延迟,对片外内存的使用效率有很大影响。Blackfin的SDRAM控制器支持多Bank的数据并发传输,因此我们要尽量把 不同通道的IO数据放在内存的不同Bank上。因此在音视频和网络数据结构的设计上,不光要保证高效的同步,还要利用Blackfin开发工具提供的特性 把数据分散在不同的Bank上。

2.片内L1内存的高效分配

传统上,DSP处理器内部的L1高速内存可以直接访 问, 存放关键代码和数据,提高算法运行效率。而MCU的L1一般全部用来做Cache,软件不能直接控制。在Blackfin等高性能处理器上,L1可以灵活 地配置成Cache或者直接访问。在一个完整的系统中,我们要兼顾到各个模块和操作系统本身,L1内存一部分用作Cache,以保证整体cache命中 率;另一部分作为SRAM用于算法的关键模块。这里需要做一些反复的调整和测试,来找出一个最优化的L1配置方案,最终目的是达到L1 内存使用效率(命中率)最大。

3.最大效率地使用DMA通道

越来越多的处理器为IO接口提供专用的DMA通道,以减 轻处理器做数据输入输出的负担。Blackfin上除了音视频接口的DMA外,还有专用的内存DMA通道。但是要最优化地使用DMA,最重要的是使用乒乓 缓冲,使处理器和DMA通道流水化工作。在数据输入,算法内部的内存DMA,数据输出等每个环节上都要使用DMA和乒乓缓冲,才能保证系统效率最高。这需 要每个驱动和软件模块都支持这样的数据结构和运行模型。

综合起来,新型处理器上往往集成了多种提高性能的机制,软件系统优化的思路,就是保证系统总带宽(如多总线,多DMA通道)和总运算单元(如多核,多乘法器)的并行化、流水化,这需要开发人员从系统和应用不同的层面来保证。

4.性能分析

系统使用的RTOS带来的额外开销主要就是定时为10ms的Timer Tick,可以忽略不计。而由于BF537高超的网络性能,网络传输所占用的处理器时间也非常小。主要的处理器时间消耗在音视频的智能分析和编码上。

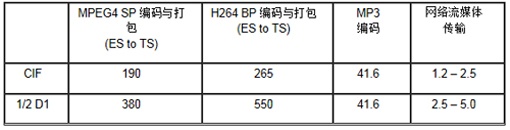

本项目可以运行在单核或双核Blackfin平台上,接收端用开源项目Video Lan Client(VLC)来接收并播放。对于单周期指令集的600MHz Blackfin内核,我们一般用600 MIPS来表示单核的总处理器能力,下表列出的部分系统模块消耗处理器能力也用MIPS来表示,如下表 (表2)所示。

表2 IP Camera 的性能测试 (单位:MIPS)

从上面的性能列表可以看出,对于系统中可以使用的每一个模块,我们都可以有一个不同参数下的性能分析,在此基础上,使用不同性能的处理器,不同的模块, 不同的编码格式,甚至不同的帧率,我们可以针对各种应用组合出不同的系统,实现产品的差异化。比如我们可以完全运行智能处理算法,只在必要的时候启动编码 模块发送关键部分的媒体流;也可以平时以低码率、低帧率运行编码模块,由智能模块动态控制提高关键帧的

美电贝尔 Lenovo 华为 智能视频监控 ADI 相关文章:

- 华为智能视频监控系统设计解决方案(09-28)

- 解读高通商业模式 华为的专利生意如何?(06-26)

- 从手机双摄像头发展看iPhone7是否会搭载?(07-15)

- 5G大战硝烟弥漫 NB-IoT抢进物联网蓝海(08-05)

- NB-IoT和LoRa的无线射频芯片厂商盘点(10-15)

- 华为推出最新远程医疗解决方案(10-29)