基于ARM+FPGA的大屏幕显示器控制系统设计

据总线8根,控制信号线5根,亮度信号线3根,输入线1根,复位信号线1根,共18根;(2)双体SRAM总线接口:地址总线15根,数据总线8根,读写控制信号2根,共50根;(3)显示控制信号输出接口:移位时钟信号1根,行锁存信号1根,行选4根;(4)显示像素数据输出接口:红、绿、蓝共3根。共计18+50+6+3=77个I/O口。为了可以使LED显示屏的尺寸增加1倍,即所需的I/O口增多,同时考用VHDL语言描述的内部功能逻辑所需的宏单元数量,需要选择256个宏单芯片,在此 FPGA选用32位的PolarPro QLlP300芯片。

2.3静态存储器SRAM的选择

外部扩展的两片SRAM,要求能满足上屏数据读取速度的要求,考虑到存储数据的宽度和容量,本设计选用ISSI(Integrated Silicon Solution Inc.)公司的IS61C1024芯片。该芯片存储容量为128 kB,8位数据宽度,最高读写速度为25 ns,电源电压为5 V,具有最高40 MHz的读写频率,可进行高速异步读写操作,无须等待时间,其容量满足一屏文字和图像数据信息的存储要求,两片SRAM采用双体切换技术来完成数据的存储和读取过程。

3 系统软件设计

3.1 ARM软件设计

根据该系统的设计需求,将软件划分如下几个模块分别形成独立的程序文件:启动代码模块、串口模块、时钟模块、温度和亮度传感器模块、FLASH 管理模块、下载管理模块和显示模块。启动代码用于初始化系统配置、初始化各个处理器模式下的栈空间,初始化目标板,引导C程序运行,用汇编语言编写;串口模块实现串口的发送、接收等基本功能;时钟模块实现RTC时间的设置与读取等基本功能;温度和亮度传感器模块实现温度和亮度控制;Flash管理模块实现外部FLASH擦除、存储、分配的管理,将显示指令和显示信息进行存储;下载管理模块负责与上位机通讯,下载显示指令和信息;显示模块负责显示指令的解析以及显示信息的提取,显示效果的处理,包括出场模式和表演模式以及各种字体字形的产生,同时负责送灰度数据给FPGA,本设计以启动代码为例阐述源代码的编写。

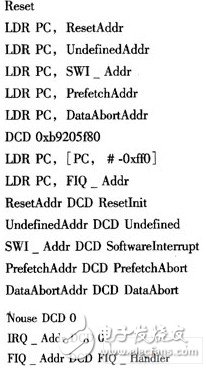

通常将启动代码划分为5个文件:startup.s、IRQ.s、stack.s、heap.s和target.c。startup.s包含中断向量表和系统初始化代码;IRQ.s包含中断服务程序与C程序的接口代码;stack.s和heap.s保存C语言使用的堆和栈的开始位置;target.c包含目标板特殊的代码,包括异常处理程序和目标板初始化程序。下面给出几个关键的初始化程序段供参考。

1.中断向量表

2.系统初始化代码

ResetInit

BL Initstack;初始化芯片各种模式的堆栈

BL TargetResetInit:目标板基本初始化

B Main;跳转到ADS提供的_ain函数处,它初始化函数库并最终引导CPU进入main()函数

3.初始化CPU堆栈Initstack(源代码略)

3.2 FPGA内部的功能模块

图4为FPGA内部的功能模块图。FPGA将ARM传送过来的信号包括灰度数据(DATA)、系统时钟(CLK)、帧同步信号(VSYNC)、行同步信号(HSYNC)、片选信号(CS2)和写信号(WRITE)送入存储器切换电路,存储器切换电路将图像数据(DAIA)分时送到静态存储器 SRAM1和静态存储器SKAM2进行存储。SRAM1和SRAM2工作在交替读写状态,即向一片SRAM写人数据的同时,从另一片SRAM中读出数据;静态存储器的读写状态由系统时钟、帧同步、行同步以及片选信号来控制。读地址发生器用于计算所需数据信息在存储器中存储的地址,以便保证LED大屏幕的正确显示,它是由移位时钟来控制产生15位读地址信号,移位时钟信号的工作频率为4 MHz。读地址发生器产生的读地址信号在移位时钟的作用下,产生4个分区锁存信号,4个分区的显示数据同时送人屏体,只有当锁存信号有效时,才点亮显示屏。从SRAM读出的灰度数据DAIA送入灰度值发生器,并根据屏体显示结构进行数据重组,转化成LED显示屏要求的上屏数据信号(红、绿、蓝灰度数据)。三色的上屏数据送入串行发送数据寄存器,并在移位时钟的作用下串行发送至屏体。在将一片SRAM中的数据转换后上屏的同时,通知微处理器发送下一屏数据。此外,ARM还发送两位亮度控制信号COMM0、COMM1和亮度数据信号COMM2。串行发送的亮度数据信号进入8位串并转换电路,在 COMM0、COMM1的控制下,产生亮度信号。

4 仿真及系统验证

使用ModelSim仿真用VHDL编写的扫描驱动电路波形如图5。从图5可知,从ARM接收到的数据data(01010101)存入到外部扩展的存储器SRAM2,m2ma是存储器2的地址线,它根据控制信号(tp1,tp2,cs2,swite)的控制作用连续增加;cm2d是存储器2的数据线,将data数据存入,则c

- LED技术50年秘史 从零走向全世界(09-12)

- 柔性OLED显示技术让未来电子产品充满无限可能(09-22)

- 有光即有网:LED Li-Fi速率可达10Gbps 将取代Wi-Fi?(08-22)

- 八大要素让你读透LED芯片(11-03)

- 无封装、无散热、无电源之后,LED还能去掉什么?(03-03)

- 电子科普:LED照明基础知识汇总(02-23)