安捷伦S系列示波器硬件设计解剖

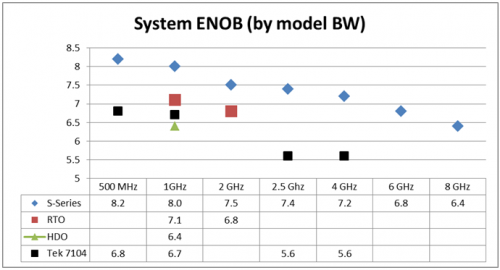

Infiniium S系列示波器使用业内带宽最高采样率最快的10位模数转换器(ADC),垂直分辨率是传统示波器的四倍(因为传统示波器大都采用8位ADC),信号细节的呈现更加精确。结合低噪声前端,S 系列示波器的有效位数(ENOB)指标遥遥领先业界,可达8位以上。Infiniium S系列示波器在500MHz 至 8GHz 带宽范围内提供多种选择、4通道DSO和16逻辑通道MSO等不同的选择,以及业内同类产品最深的存储器:所有通道标配50Mpts存储器,半通道模式下可达到100 Mpts,选件可达800Mpts。

S系列示波器配有业界最全面的各种测量应用软件,采用的电脑主机板是8GB RAM 配置,能够在所有工作模式下保证快速响应。固态硬盘实现极速启动并增强可靠性。15英寸(38.1 cm)多点触控电容屏,不仅显示尺寸为行业之冠,而且在操作体验方面引领业界未来方向。

图1

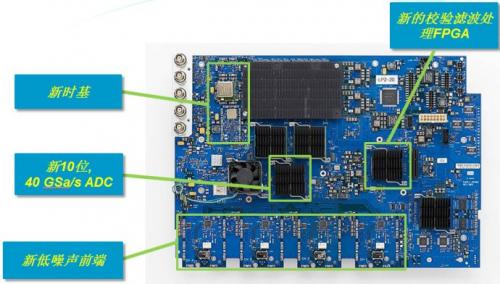

=S系列示波器设计的比较简洁,内置一块示波器采集板和一块工控机主板,主板的CPU是Intel的i5四核3GHz处理器,8GB内存,运行嵌入式标准的Windows7 64位操作系统。示波器采集板是关键部件,如图2所示。采集板使用了20层的PCB,并且使用了低损耗的Rogers板材。使用了单芯片40GSa/s ADC(有三种工作模式:单通道40G,双通道20G,四通道10G)使得芯片成本降低到最小(多个ADC需要多个FPGA做内存管理和信号处理,成本相对较高)。下面分别对各个部分进行解剖。

图2

如图3所示的ADC是业界第一个40GSa/s、10位的ADC,在自定义的33mm BGA封装上封装了2个芯片,左边的是130nm的BiCMOS buffer IC,右边的是65nm的CMOS(9mm

图3

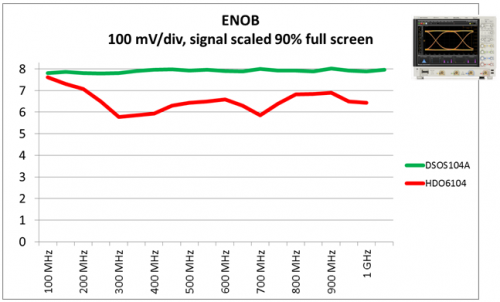

以1GHz带宽示波器为例,输入不同测试正弦波的ENOB图表如图4所示(测试时,示波器设置为100mv/div,输入测试正弦波幅度为7.2格)

图4

与市场已经有的1GHz高清示波器做比较,有效位结果如图5所示(对比的是LeCroy的HDO6104)。影响有效位的不仅仅是ADC,还有前端放大器,S系列示波器由于设计了低噪声的前端,所以有效位较高。

图5-1

图5-2 业界同类示波器的有效位比较

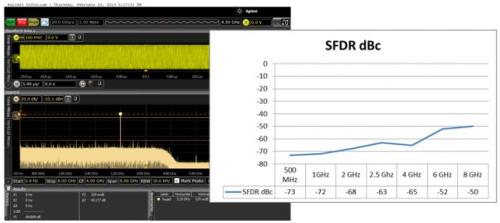

这颗ADC另外一个优点是非线性设计的较好,500MHz时SFDR可以达到-73dBc,不同频率的SFDR见图6所示。

图6

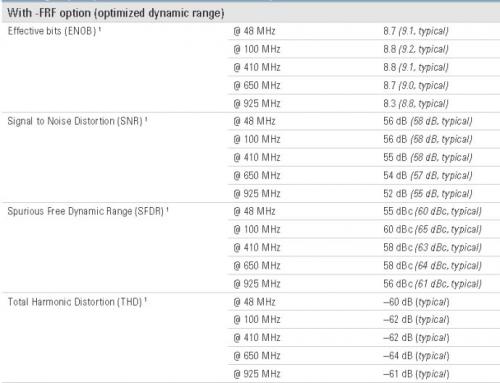

现在业内最高性能的高速数采卡是Agilent的M9703A,12位ADC,1.6GSa/s(交叉3.2GSa/s)采样速率,对于FRF(1GHz 带宽选件)的性能指标如图7所示。对比可见,1GHz以内带宽时,S系列示波器与其相当,但是因为有过采样能力,S系列示波器的动态范围还要大些。

图7

2.低噪声模拟前端

为了发挥10位ADC的性能,特别设计了一个低噪声模拟前端,这个低噪声前端带宽可达8GHz(对外连接器也是镀金的精密PBNC)。支持50ohm和 1Mohm输入路径,并且每个路径都支持带宽限制滤波器,以减少不需要的噪声。在1GHz带宽时,只有90uV的噪声,并且硬件支持2mv/div的垂直 灵敏度。使用电子衰减器减少噪声和增加可靠性。并且通过软件软件license可进行带宽升级。放大器,模拟滤波器和带宽升级都通过图中的大的芯片实现, 这个芯片是130nm BiiCMOS集成电路。

图7-1 低噪声模拟前端部件(侧面)

图7-2

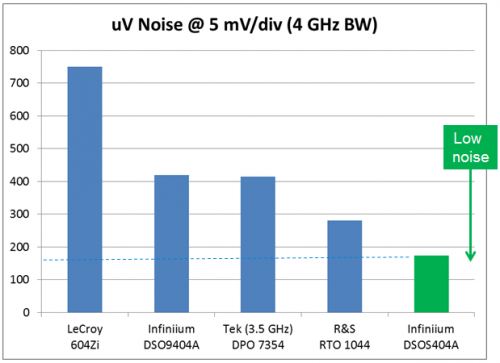

以业界常见的4GHz带宽示波器为例,低噪声对比如下图8所示。

图8

3. 校验滤波处理

个人认为图1中S系列示波器捕获板圈起来的"新的校验滤波处理FPGA"的位置是错的(这个图是来自美国研发部门),这个FPGA应该与以前示波器一样, 在ADC后面,执行内存管理,校验滤波处理,显示刷新加速处理等功能。现在多了一个FPGA,应该未来有更广泛的用途,比如:执行FFT运算,抖动测量运 算,函数运算,DDC运

- 安捷伦TD-SCDMA测试解决方案(06-03)

- 安捷伦科技展示全面的毫微微蜂窝基站测试能力(11-15)

- 安捷伦科技推出电气一致性测试软件和测试夹具(01-08)

- 安捷伦科技E6651A 移动WiMAX 测试仪系列新增功能测试特性(04-06)

- 安捷伦科技扩展 PXA 信号分析仪的功能(01-26)

- 安捷伦科技发布Medalist i3070 系列5 在线测试平台(08-04)