基于ADSP-BF533的数字通信信号发生器设计与实现

度加权,然后和噪声叠加,再通过PPI DMA输出到DAC2来产生干扰与噪声的混合波形。其中PPI时钟PPI_CLK信号均由各DSP的定时器产生。

两个DAC的位数是14位,并且设置为4倍插值方式,即DAC输入数据率为10MSPS,输出转换速率为40MSPS。DAC转换需要的时钟与PPI_CLK共用,DAC连接在BF533PPI总线的低14位PPI13~PPI0。基带码流通过DSPl的PPI15引脚输出,同步信号通过DSP1的PPI14引脚输出,经过74AC11244驱动输出波形。

DAC输出的模拟信号后经过AD8054缓冲放大,再经信号和噪声合成后分为两路,可作为测试波形和信号源。

若需要模拟通信信号环境,需要在微型计算机中计算多种信号的叠加数据,然后传送到通信/通信信号环境数据存储器(SDRAM1)中,其它过程均与通信方式相同。此模式下不能测试基带码流,但仍可测试同步信号。

3 系统软件设计

系统中的微型计算机采用Windows 2000/XP操作系统,其USB驱动程序由DDK开发,控制应用程序可通过VS2005进行开发。计算机可根据用户的输入参数产生2ASK、2FSK、8FSK、2PSK、2DPSK、QPSK、QDPSK等通信信号或者它们几种混合的通信环境信号,窄带高斯白噪声和噪声干扰、局部频带干扰、梳状干扰、相关干扰信号.并可将数据打包后通过USB接口发送到信号发生板卡。随后由计算机通过发送控制命令字的方式来处理数据,主要是开始输出波形、停止输出波形,更新波形数据,更新通信信号环境波形数据,更新干扰/噪声数据,更新信噪比或干信比。

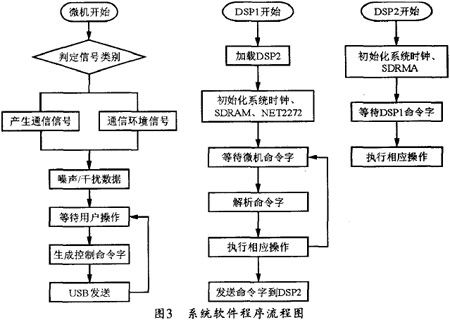

系统的软件设计主要是针对BF533进行编程。Blackfin系列DSP在软件方面支持C语言和汇编语言,同时支持二者的混合编程。C语言程序结构好、可读性强、易移植,但对于中断的处理速度慢。汇编语言处理速度快但可读性差,不易调试。C和汇编混合编程结合了各自的优势,能构造出结构好且执行速度快的程序。本系统的软件程序流程图如图3所示。另外,在编程过程中主要注意以下事项:

(1)无论用C还是汇编,系统中只有一组相同的寄存器可供使用,因此要使用这些寄存器,子函数必须先保存,返回之前恢复。

(2)要严格按照寄存器的类型来使用,不同类型的寄存器不可混用。

(3)尽量节省寄存器资源。

(4)为了提高代码运行的速度,要善于使用并行指令。

在本系统中,中断与DMA方式运用较多,主要用到了PF中断、MDMA中断、SPI DMA中断和PPI DMA中断,系统中断控制器可控制所有的系统中断,并且管理他们的优先级。DMA不需要内核参入,在DMA运行中内核可以用于计算也可以响应中断。

系统上电后,DSP1先从Flash中读取自身的加载代码,然后再从Flash中读取DSP2的加载代码通过SPI接口传送到DSP2加载DSP2,最后再初始化系统时钟、SDRAM、NET2272USB控制芯片,进入等待微机用户指令状态。

4 结束语

该数字通信信号发生器只需要在通用微机或者PC机上安装软件即可实现,其成本低,效率高,实时性好,特别是在通信对抗信号源模拟方面,更是显示了无可比拟的优越性。

- 广播电视常用的数字视频编码技术 (11-02)

- 基于H.264视频压缩快速运动的估计算法(02-01)

- 基于OMAP3的视频解码器的通用解码方案 (07-26)

- 数字语音解码器的低功耗设计策略(08-23)

- 数控电位器在频率可调信号源中的应用(08-30)

- 信号完整性与电源完整性的仿真分析与设计(08-31)