航天科工二院23所成功自研新芯片 填补频综芯片研制空白

时间:05-04

来源:中国航天科工集团公司新闻中心

点击:

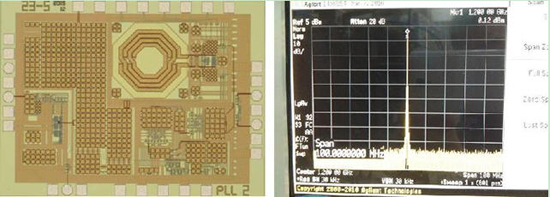

近日,中国航天科工二院23所首次自主研制的L波段PLL(Phase-Locked Loop,锁相环)芯片取得成功。该芯片是23所研发的首款PLL芯片,填补了23所在频综芯片研制上的空白,并朝着芯片产品应用化迈出了关键一步。

锁相环是频率源,是整个雷达系统中的关键技术,是各类型号产品中不可或缺的组成部分。研制PLL芯片,可以有效减小接收、频综系统体积,降低成本。对于实现核心技术的自主可控,具有十分重要的意义。

此次研发的PLL芯片,体积小、功耗低、集成度高,部分性能指标优于国内已有的同款芯片产品。该芯片可以应用于多款雷达的接收、频综、模拟器系统,应用前景十分广阔,并为未来进一步开发时钟芯片和接收频综SOC集成打下了坚实的基础。

上一篇:Altera演示Stratix 10 FPGA和SoC双模56-Gbps PAM-4和30-Gbps NRZ收发器技术

下一篇:NI AWR软件产品组合新添AntSyn技术,用于天线综合及优化

下一篇:NI AWR软件产品组合新添AntSyn技术,用于天线综合及优化

- 中国航天科工太赫兹光谱仪面世(01-14)

- 中国航天科工研发GPS探空仪整装待发走出国门(02-20)

- 我国首部低空连续波测风雷达问世 为飞机起降“保驾护航”(09-05)

- 航天科工电磁辐射计新产品填补市场空白(01-20)

- 航天科工三院33所成功自主研制测量用ASIC芯片(04-08)

- 航天科工成功研建“最高速度示波器校准装置”(01-19)