基于PLL技术的合成频率源设计

不稳定度也常用时域阿仑方差σ2y(2,t,t)及频域相对单边带功率谱(简称功率谱)XXXX表征。

它们的定义为:

式中:XXXXX为为测量采样时间XXX的相邻二次测量测得的频率平均值。

式中:PSSB(f)为一个相位噪声调制边带在频率为f处的功率谱密度,P0为载波功率。

.4 系统各组成部件相位噪声分析

锁相环频率合成器主要由倍频器、放大器、分频器、混频器、鉴相器、振荡器等基本电路组成,还包括辅助捕获电路、跳频控制电路和电子开关等,它们都会不同程度地对频率合成器引入噪声。

4.1 振荡器

振荡器的噪声主要决定于谐振电路的有载Q1值、谐振电路噪声以及振荡器件本身的噪声。振荡器噪声主要由4部分组成:

(1)由闪烁噪声调频产生的相位噪声。

(2)由散弹噪声和热噪声调频产生的相位噪声。

(3)由闪烁噪声调相产生的相位噪声。

(4)由散弹噪声和热噪声调相产生的相位噪声即白噪声。

VCO相位噪声与晶体振荡器相比有两点不同:其一VCO谐振回路Q值低,VCO工作频带越宽,Q值越低;其二VCO谐振回路存在变容二极管,它具有与振荡器件一样的噪声。此外,VCO相位噪声还与压控调谐灵敏度成正比关系。

由于谐振回路Q值低,因此宽带调谐VCO近端相噪较差,比没有电压控制电抗电路的振荡器高出20 dB~40 dB。但由于VCO输出信号功率比晶体振荡器大,VCO远端相位噪声反而比晶体振荡器倍频后相位噪声低。

4.2 外部噪声

N倍频后,外部噪声将提高20lgNdB,折算到器件输入端的内部噪声也将提高20lgNdB。因此倍频器设计时应注意降低其内部噪声。

4.3 分频器

当信号通过分频器时,输入端的噪声通常要减小20lgNdB,如果分频系数很高或输入信号相位噪声极低则最低限度的噪声决定于分频器噪声以及接在分频器后的有源电路的噪声。

5 锁相源的具体设计和实现

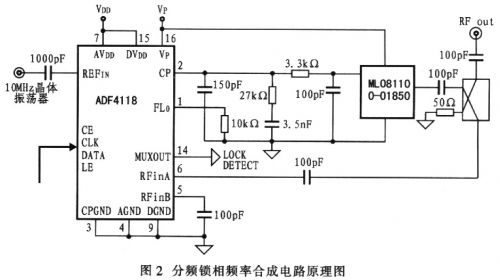

该频率源设计中,分频鉴相器选用美国ADI公司的ADF4118;压控振荡器VCO选用M/A-COM公司的ML08l100-01850;环路滤波器采用三阶RC低通滤波电路组成,其电路原理如图2所示。

锁相源设计中的关键是环路滤波器的设计。最简单、最廉价的低通滤波器就是基本的RC低通滤波器。这种滤波器没有精确的截止频率,典型的下降斜率是6 dB/lO倍频程,因此电路的-3 dB点应设计成接近电流信号的基频。较好解决方法是用一个三阶RC滤波器,其原理如图3。

当锁相环的环路滤波器通频带较窄且捕捉带也较窄时,利用锁相环良好的跟踪特性,可实现高频率输入信号的窄带滤波;可在几十赫兹的频率上实现几十赫兹甚至几兆赫兹的滤波,从而将混入输入信号中的噪声和干扰滤掉,这是其他滤波器难以做到的。

6 测试数据

该锁相源设计成功后笔者对其进行了测试,输出频率1 835 MHz,输出功率-4.2 dBm,相位噪声的测试结果如表2。

由表2数据可得在输入频率为1 835 MHz时,输出功率为-4.2 dBm,相位噪声为-75 dBc/KHz,杂散抑制为-85 dBc,完全符合预期设计的技术指标。

7 结束语

针对移动通信基站和直放站射频子系统对本振源的要求设计了该频率源。根据实验结果可以看出,使用ADI公司的锁相环(ADF4118)得到的锁相源与相关资料介绍的使用飞思卡尔公司MCl45系列锁相环的锁相源相比,在1 835 MHz频率点上相噪要好10 dB~20 dB、同时用在移频模块中相应相噪要好10 dB~20 dB。

该设计的成功进一步验证锁相频率源具有频率稳定度高、频谱纯、寄生杂波小及相位噪声低等优点,该方法设计简单、可靠性高、抗干扰性强。

.

- 基于AD8302的相位差测量系统的改进和设计(05-09)

- 基于DDS频率源的设计与实现(04-24)

- PLL技术简介及其在合成频率源中的应用(03-27)

- 满足嵌入式系统电路特性测试需求的JTAG技术(04-25)

- 全方位解析万用表在电子系统测试测量中的使用技巧(10-19)

- 综合电子系统集成测试解决方案(02-06)