基于DSP的1553B总线通讯检测仪的设计

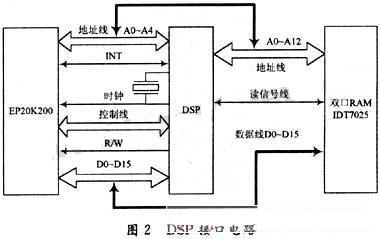

总线的接口技术的把握,其主要接口电路如图2所示。

由DSP接口电路图可以看出,DSP模块为整个系统提供了时钟电路,DSP芯片的中断由EP20K200产生,一方面通知F206读取数据,一方面通知DSP进行错误处理,由于DSP芯片的流水线操作方式,数字信号处理速度功能强大,满足了1553B协议传输速率大的特点。

3.4 双口RAM和显示模块

由于在高速数据处理和采集系统中容易造成数据堵塞现象,高速数据接口的设计对整个系统数据传输的畅通起着重要的作用,该设计中采用的美国DDC公司的8k双口静态RAM IDT7025解决了数据堵塞的问题。

在该设计中显示模块采用了一种内存接显示模块的硬件连接方式。DSP将欲显示的数据送入双口RAM,51单片机不断扫描内存,根据内存中的数据做出相应的处理,不断刷新显示屏上的内容,双口RAM的BUSY信号线为避免左右端口同时对同一存储单元写操作提供了硬件支持。设计中液晶显示模块采用16×16点阵的中文显示模块。

4 系统软件设计

该1553B航空电子总线检测仪软件设计主要包括3大部分,用以驱动数据采集板卡,完成对各寄存器的配置,实现数据的收发检测。

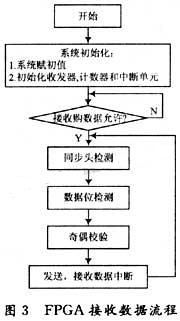

4.1 FPGA控制程序

该部分采用硬件描述语言VHDL进行编程,用Synplify进行综合,以及采用Max+Plus II进行时序仿真,在FPGA上实现的MIL-STD-1553B总线接口中的曼彻斯特码编码、解码器,该逻辑可由状态机实现,可划分为4个状态进行;第1个状态行是空闲状态,当检测到数据跳变沿时,进入第2个状态;第2个状态为有效同步字头检测状态;当检测到有效同步字头时,启动第3个状态,用锁相环分离时钟,进行码型转换;当数据有效时进入第4个状态,进行并/串转换及奇偶校验。FPGA接收数据流程如图3所示。

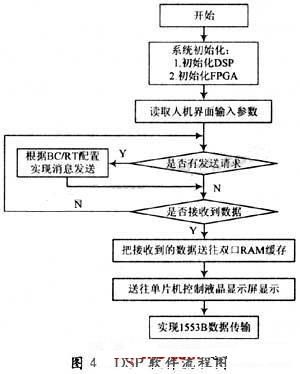

4.2 DSP模块控制程序

DSP部分的软件采用C语言和汇编语言混合编程,即具有C语言可移植性强的特点,又具有汇编语言执行速率快和直观的特点,该设计中DSP软件设计主要完成对FPGA和其内部通讯寄存器初始化;向FPGA发送数据时的控制命令操作,接受数据时命令字,状态字的处理,以及通知FPGA接受数据等,是整个系统控制的核心部分。图4给出DSP软件控制流程图。

5 结语

基于1553B总线的航空电子检测仪主要用于部队航空电子设备在线和离线检测,同时满足BC和RT的功能,PDA的设计对检测也提供了极大便利,当然由于设计处于样机阶段,还存在一些不完善的地方,今后的改进空间还比较大。

作者简介:朱明君 朱俊,空军工程大学 陕西西安。李伦,中国人民解放军95430部队 四川成都。

- 基于DSP与AD9852的任意信号发生器 (11-03)

- 多通道数据采集系统(11-12)

- 基于DSP和以太网的数据采集处理系统(01-01)

- 用矢量信号分析仪检测非线性失真(04-29)

- 利用虚拟仪器进行数字信号处理设计(02-11)

- 基于μC/OS-II的电力参数监测仪设计(02-23)