FPGA在TD-SCDMA通用开发平台中的应用

成;A/D模块到FPGA的数据接口根据MAX19700芯片的数据手册来编写。以上三个接口必须在FPGA端模拟出来,才能完成FPGA与其他器件之间的数据控制和传输。

3程序设计

3.1McBSP接口

McBSP(MultiehannelBufferedSerialPort),即多通道缓冲串口。TMS320VC5510芯片有3个高速、全双工MeBSP串口,McBSP串口是在标准同步串口的基础上扩展而来,它能提供强大的同步串口通信机制,速度可达100Mb/s。基于MeBSP的优异性能,McBSP被用来在FPGA和DSP之间传输有效数据信息。

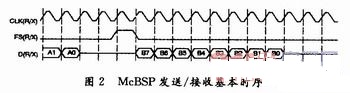

McBSP包括一个数据流路径和一个通过6个引脚连接到外部器件的控制路径,这6个引脚分别是DX(数据发送)、DR(数据接收)、CLKX(发送时钟)、CLKR(接收时钟)、FSX(发送帧同步)、FSR(接受帧同步)。有效的数据经McBSP串口通过DR和DX引脚和外部设备通信,同步控制信号则由CLKX,CLKR,FSX,FSR等4只引脚来实现。图2中简要画出了McBSP发送/接收的基本时序图。

McBSP的具体实现在参考文献中有极为详细的介绍,这里不再赘述。

3.2SPI接口

SPI接口是由Motorola公司推出的一种双向、四线串行外围设备接口,专门用来和可以提供四线串口的外部设备传输数据。四线串口信号包括时钟信号、设备使能信号、数据输入、数据输出,传输串行数据时高位优先。

SPI可以使用MCU_DSP协议或者DMA协议在主/从模式下运行。在主模式下,它提供5个片选,支持多达5个串行设备,其中4个片选对外部设备,此模式下的最大数据传输速率是19.2Mb/s或12Mb/s;在从模式下,SPI有它自己的片选,数据输出的时钟由拥有较低速率的外部设备提供。SPI发送/接收基本时序图如图3所示。

由于内部移位寄存器是基于一个环形(FIFO规则),故读、写过程必须时刻同步;只要任一发送时钟产生,数据发送就会启动;在移位寄存器时钟SRCLK的上升或下降沿,发送或接收的数据被移入或移出。

3.3与MAX19700的接口

根据Maxim公司的MAX19700芯片的数据手册,该芯片的工作时钟为5.12MHz,它提供了双10b,7.5MSPS的Rx(ADC),Tx(DAC)通路。图4描述了A/D转换时的时序图。

MAX19700芯片的接收或发送开关是由专用引脚T/R来控制的;芯片的SPI接口用来接收配置数据,不受专用引脚T/R的控制。

3.4功能模块设计

Turbo编码/译码、Viterbi译码、FIR滤波器以及快速傅里叶变换和反变换(FFT/IFFT)都可以利用Xilinx公司提供的ipcore来实现。因为这些模块都非常成熟,其可编程性能好、算法先进、延迟小、占用资源少,直接使用要节省很多时间,可以缩短产品的开发周期。当然,Turbo编码/译码器和Viterbi译码器要购买才能商用,但在前期测试时可以申请评估版本使用。

3.5资源利用率

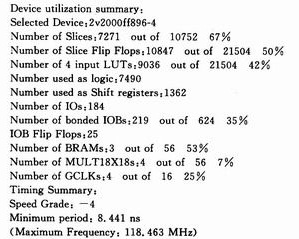

以上接口程序和功能模块是在Xilinx的集成开发环境ISE9.1中,使用VerilogHDL硬件描述语言完成代码编写的zxzb,综合结果如下:

一般而言,Xilinx芯片的资源利用率看Slice和SliceFlipFlops两项数据就可以,这两项数据最好保持在50%~70%之间。这样,既可以最大限度地发挥芯片的性能,也为以后的平台拓展留下足够的空间。从上面的数据可以看出,Xilinx芯片的资源利用率是非常理想的。

4结语

随着FPGA各项性能的不断提高,已经越来越显示出它在数字信号处理中的优越性;本文在一种基于"软件无线电"技术的TD-SCDMA通用开发平台中,以FPGA作为DSP的协处理器,用来完成Turbo编码/译码,Viterbi译码以及快速傅里叶变换和反变换(FFT/IFFT)等数据量大、重复性强、速度要求高的数字信号处理运算,使平台具有很好的硬件灵活性、软件可编程能力和较低的系统成本。测试表明,平台的各项性能均能够达到3GPP的标准,具有很好的市场前景。

- TD-SCDMA系统终端CC实体的一致性测试(10-27)

- R&S公司的TD-SCDMA测量解决方案(01-01)

- TD-SCDMA多模终端生产测试探讨(11-05)

- 智能天线的测试(01-18)

- CDMA/GSM手机在线功能测试(11-25)

- 什么是TD-SCDMA?(06-03)