DDR3测试的挑战及解决方法

2. 测量Cross-point Timing

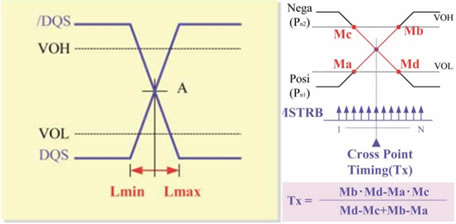

DDR3的CLK和DQS均采用差分信号。差分信号的交点(cross-point)定义了数据周期宽度。采用与测量Tr/Tf相同的方法,在一对差分信号的两个通道上分别进行测量,得到下图中四个参考点(Ma, Mb, Mc, Md)的出现时间。然后,借助公式可以计算出cross-point的位置(Tx)。

图 7 Multi-Scan Strobe功能--测量Cross-Point的出现时间

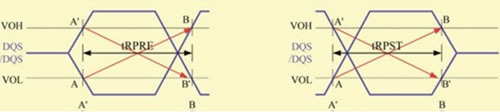

3. 测量Preamble/Postamble Timing

对于DDR3芯片,在DQ管脚输出数据之前,DQS信号会提前一段时间由高阻态变为低电平,这段时间为tRPRE;DQ完成数据传输之后,DQS信号会继续维持一段时间的低电平,再变为到高阻态,这段时间称为tRPST。

图 8 Multi-Scan Strobe 功能--测量Preamble/Postamble时间

以DQS信号为例,tRPRE可以表示为A点到B点之间的距离,tRPST可以表示为A’点到B’点之间的距离。与Tr/Tf的测试类似, Multi-Scan Strobe功能可以方便地得到测试结果。

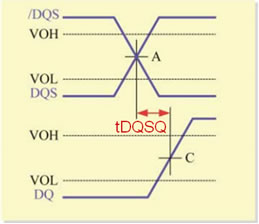

4. 测量 tDQSQ和Jitter分布

tDQSQ定义为DQS差分对的cross-point到 DQ输出的时间延迟。以往对于tDQSQ这一参数的Margin测试,通常采用调整采样信号时间沿,反复扫描的方式。这种方式的测试时间相对较长。下图是 tDQSQ的示意图,图中A点和C点之间的时间延迟就是tDQSQ。

图 9 Multi-Scan Strobe 功能--测量tDQSQ

参考前文中Preamble/Postamble Timing的测试方法, Multi-Scan Strobe 功能可以很容易地获得A点和C点的时间延迟。除了测试效率以外,测试结果的精确度也是我们必须考虑的。由于tDQSQ参数考量的是DQ的输出和DQS的输出在时序上的关系,其数值受到DQ和DQS jitter的影响。在信号频率较低,数据周期较宽的情况下, jitter的影响可以忽略,直接计算A点到C点的距离就可以得出tDQSQ。但是随着数据周期的减小,A点和C点出现位置的抖动变得不可忽略,jitter对数据窗口宽度的影响日益显著,给tDQSQ的测试带来了困难。

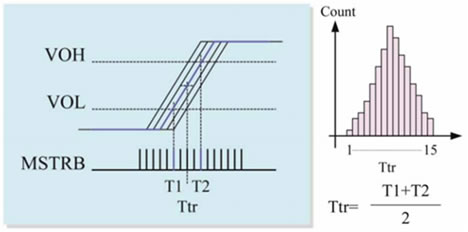

图 10 Multi-Scan Strobe 功能--测量Jitter

为了克服jitter带来的不利影响,Multi-Scan Strobe功对芯片输出信号的多个周期的进行采样,记录每次采样的结果(如信号的50%点,Ttr),并得到其正态分布。上图右下角,取Ttr分布最高处的点为DQ的50%点。同样,DQS差分对的cross-point也取分布最高处的时间点。此时,tDQSQ可以表示为两个分布最高点处的时间差。

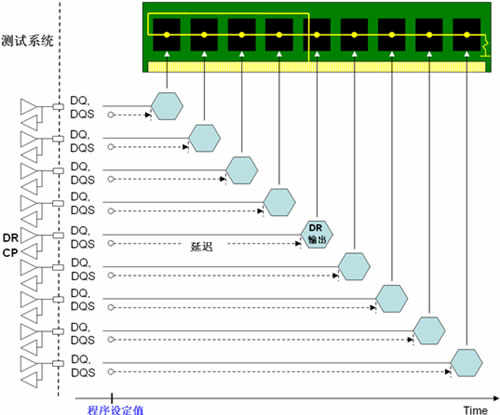

•提供Per-Pin Offset功能(对Fly-by结构进行时间补偿)

系统提供了Per-Pin Offset功能,它可以灵活调整测试通道中波形产生的时间以及数据比较的时间,从而补偿Fly-by结构带来的延时。

图 11 T5503的Per-Pin Offset功能

•提供128 DUT/SYS的并行测试能力

根据ITRS的预测,随着测试频率的增长,由于测试接口布线复杂性的提高,在一个测试头(STN)上实现128DUT并行测试将是一个挑战。T5503配备有一个测试头,具备128DUT/STN的测试能力,可以有效提高测试效率、降低测试成本。

•具有多Site、低功耗、体积小的特点

系统的测试头由两个Site构成,每个Site可独立工作,允许多个用户同时使用同一系统。此外,得益于先进的系统集成技术,系统的体积和功耗削减了40%左右。

图 12 T5503的外观

总结

ADVANTEST的T5503系统可以满足用户对DDR3高速测试的需求。

ADVANTEST在存储器测试方面拥有着丰富的经验,一直致力于为客户提供优质、高效的解决方案。ADVANTEST专注于生产高品质的测试系统,针对客户需求和市场变化不断地推出有竞争力的产品,帮助客户解决研发和生产中遇到的问题。

- 泰克的DDR测试和验证解决方案系列增加两项新功能(11-13)