基于Web和硬件可重构技术的远程抄表设计

引言

随着计算机技术的发展,远程抄表技术逐渐得到广泛的应用。通过实行一户一表以及自动远程抄表,可以做到及时、准确地进行数据采集,并且提供了一种对欠费用户进行有效管理的手段。远程抄表系统通常主要由计量仪表、数据集中器、通信网络以及抄表程序四个部分组成。计量仪表完成信息转换、数据存储功能,并支持通过本地通信网络与数据集中器进行数据交换。数据集中器完成数据汇聚功能,并能与抄表程序进行远程数据交换。抄表程序则借助通信网络从数据集中器获取计量数据,并存入数据库中。在绝大多数远程抄表系统中,计量仪表通常没有太多差别,而对于抄表程序以及紧接其后的各种数据查询、统计等操作都是典型的数据库应用系统,差别也不大。相比之下,通信网络以及与之紧密相关的数据集中器则是不同系统之间差异较大的地方,同时也是技术上的难点。

针对以上问题,本文提出了一种基于Web和硬件可重构技术的远程抄表系统结构。软件方面,它在数据集中器中利用一个嵌入式Web服务器来负责数据的传送任务,采用HTTP作为通信协议。客户端则是操作系统自带的Web浏览器,从而可以解决各个系统之间由于通信协议不同而造成的兼容性问题,而且节省了抄表客户端的软件开发成本。硬件方面,采用硬件可重构技术和基于IP核的设计方法,在单个FPGA芯片上实现了数据集中器。即使将来需要对系统进行改进和升级,也只需对FPGA芯片的配置文件进行修改,而不必报废整个硬件系统,从而保护了已有的硬件投资,降低了系统的维护成本。另外,数据集中器上的通信接口也可以借助硬件可重构技术很方便地更改,因而能够适应各种硬件环境。

远程抄表系统的体系结构

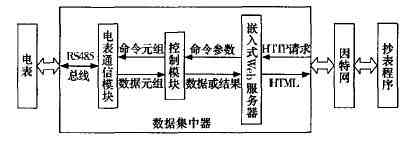

基于Web的远程抄表系统的体系结构如图1所示(以电表为例)。

图1 基于Web的选程秒表系统的体系结构

它由三个部分组成,分别是抄表客户端程序、数据集中器以及分布在各家各户的电表。抄表流程如下:首先由抄表人员使用抄表客户端程序向数据集中器以HTTP协议的形式发送抄表请求,该请求通过因特网到达数据集中器后,会首先被一个嵌入式Web服务器进行处理。嵌入式Web服务器将返回一个HTML文件给客户端,要求用户输入命令类型(例如,是抄数据还是执行相关控制操作)、电表编号以及附加数据。当用户填完表单后,这些数据将依照HTTPPOST协议发送给数据集中器中的嵌入式Web服务器。随后,相关的命令和数据参数抽取出来,送给数据集中器的控制模块。控制模块将对命令参数进行判断和安全性检查,然后生成相应的命令元组,以便控制和读取数据。电表通信模块完成与电表之间的通信任务,负责将命令元组发送给电表,并读取执行结果。当执行抄表操作时,数据将被电表通信模块以数据元组的方式返回给控制模块,然后按照固定格式被组装为一个字符串,并交给嵌入式Web服务器。嵌入式Web服务器将这些数据插入到预先设计好的HTML文件模板中,随后将其通过因特网返回给客户端的抄表程序。

硬件设计

从图1中可以看出,数据集中器是系统中的关键部分,一方面它需要按照《DL/T64521997:多功能电能表通信规约》通过RS485总线从电表处采集数据,并执行各种控制任务;另一方面它必须能够解释以HTTP形式发送过来的控制命令,并将执行结果以HTML文件的形式返回给抄表客户端。

本文在进行硬件设计的时候采用了基于IP核的设计方法,并将数据集中器的大部分功能在单个FPGA芯片上予以实现。设计电路原理图之前,必须根据系统需求选择合适的IP核。所谓IP核,是指那些以硬件形式(硅片版图)或者软件形式(用Verilog、VHDL描述的RTL或者门级模型)存在的、具有特定功能的硬件电路。IP核通常分为硬核、固核与软核三种。根据系统的硬件开发环境以及性能需求,本文选择了Altera公司开发的一系列软核产品,它们是用Verilog语言所描述的硬件模块,允许用户根据需要对各种参数进行配置,如数据通路带宽、优先进行速度优化还是资源优化等,因而应用非常灵活。系统所用到的软IP核产品有Nios CPU、ROM、RAM、定时器、通用异步收发器UART,以及用于外部功能扩展的Avalon总线模块,并将Nios CPU配置为32位字长模式,拥有256个通用寄存器,工作频率33MHz;UART配置为14400bPs的波特率,8位数据位,2位停止位,无奇偶校验。在确定了IP核并进行相应设置后,需要设计系统的电路原理图。图2表示了由各个IP模块组成的数据集中器内部硬件结构,其中的ROM用于存放用户程序,RAM作为程序运行时的存储空间,定时器为实时操作系统提供时钟中断功能,外部总线接口和UART负责与系统外部进行通信。它们将通过一条内部总线与Nios CPU相连,这样就构成了一个完整的嵌入式硬件系统。设计电路图后的下一步工作是选择合适的实现载体。基于IP核的设计方法通常使用FPGA芯片或者直接在硅片上实现。本文采用的是Altera公司APEX20KE系列FPGA芯片,能提供8000个左右的逻辑块资源和多达400Kb左右的ROM和RAM存储空间。由于FPGA芯片具有可反复更改的特性,因此有助于硬件系统的改进和不断升级。另外,通过对通信接口进行重构,例如将UART改为CAN总线控制器,可以使系统能与更多的硬件环境兼容。

- 吉时利为3700系列系统开关/万用表固件增加图形绘制工具包(05-24)

- 基于VRML的虚拟机房的设计与实现(06-07)

- 云计算与虚拟化的融合 (10-04)

- Web网络传感器的远程数据采集系统设计(07-07)

- 一种WLAN自动化测试平台的设计及实现(03-27)

- 嵌入式智能设备的测试研究方法(05-28)