用内部逻辑分析仪调试FPGA

时间:02-13

来源:

点击:

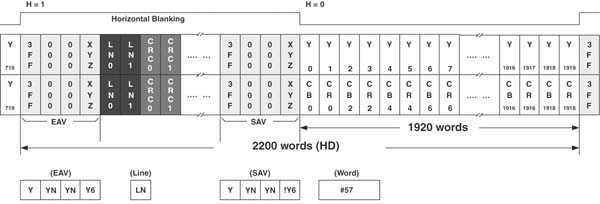

图2 SDI HD数据流实例

为了调试找到这种数据需要寻找值的时序,再找特殊值,然后结束序列,最后在捕获数据前数时钟的数目。为了理解是如何做的,必须查看具体的实现过程。莱迪思的Reveal硬件调试器使用触发单元和触发表示以决定触发点。触发单元是一个比较器,触发表示允许触发单元和序列值组合在一起。

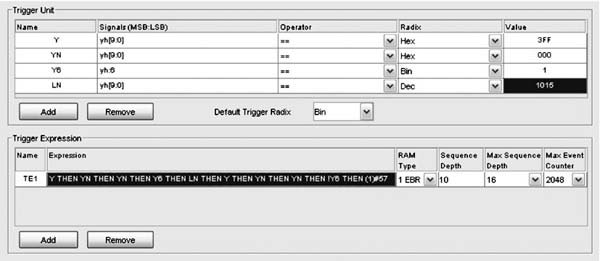

对于这个SDI实例,用3个触发单元来定义EAV和SAV序列,另外的触发单元用于线数,最后在发现数据前的一个计数声明用于等待。触发建立的实例如图3所示。这个设置可以用来寻找任何要求的线数和像素,因为线数触发的值和计数可以动态地改变。

图3 触发设置的实例

结论

工程师将继续使用外部逻辑分析仪,因为用它分析系统级功能时是很有价值的。但是用于内部FPGA调试需要连接到电路板,信号的数目受到了限制。而内部逻辑分析仪在可用信号数目方面提供了很大的自由度,但是在触发逻辑和跟踪存储器方面受到约束。然而小心地使用触发选项使内部逻辑分析仪在精确的时间开始捕获数据,要最大化可用的资源。这个例子中,需要分析在SDI视频信号里特殊的像素(线和字)的复杂实现被分解成简单的元素,这种方法提高了效率。这个例子只是浏览了内部逻辑分析仪的使用和应用。由于FPGA设计复杂性不断增加,针对功能验证和调试,内部逻辑分析仪和类似的工具受到了设计者的青睐。

- 正确选择和使用逻辑分析仪:逻辑分析仪原理(12-01)

- 逻辑分析仪在数字电路测试中的触发选择(04-27)

- 了解逻辑分析仪(05-16)

- 逻辑分析仪应用于ADC及相关领域(07-13)

- 用逻辑分析仪进行串行闪存测量(04-15)

- 使用MSO2000和DPO2000调试串行总线(05-01)