基于FIFO IDT7202-12的数字存储示波器

C8051F具有标准8051兼容的I/O端口。有的端口在某些器件中没有引出脚,这样的端口可用作通用寄存器。I/O端口的工作情况与8051相似,但有些改进。每个端口I/O引脚都可以被配置为推挽或漏极开路输出。在标准8051中固定的"弱上拉"可以被禁止,这为低功耗应用提供了进一步节电的能力。最突出的改进是引入了数字交叉开关。这是一个大的数字开关网络,允许将内部数字系统资源分配给端口I/O引脚。与具有标准复用数字I/O的微控制器不同,这种结构可支持所有的功能组合。可通过设置交叉开关控制寄存器,将片内的计数器/定时器、串行总线、硬件中断、ADC转换启动输入及微控制器内部的其他数字信号配置为出现在端口I/O引脚。这就允许用户根据自己的特定应用选择通用端口I/O和所需数字资源的组合。

4 显示模块

本设计采用PC显示波形,主要是因为通过应用VB能很容易地实现波形的显示,并且还能将波形数据存储到硬盘当中,以实现示波器的存储功能。但是要注意以下几点:

①波形消隐。在实际使用时一般需要连续显示波形。连续显示波形时,在显示下一幅波形之前,首先需要将上一幅波形清除或消隐。VB的图片框和窗体提供了CLS方法,可以实现波形的清除;但在连续显示和清除波形时,存在严重的闪烁现象。

将显示波形的图片框或窗体的DrawMode属性在属性框中设置成13-Copy Pen,或者在程序中使用类似Picturel.DrawMode =vbXorPen的语句将画笔设置成"异或笔",显示波形后经过二次重画即可消隐已经显示的波形。整幅显示一整幅消隐波形一样可出现一定的闪烁,但通过消隐一条线段一显示一条新线段的方法可彻底消除闪烁问题。该方法对波形显示区中的文字或其他控件均不会造成影响。

②双通道问题。在VB当中,曲线是利用连接"当前点"而生成的。要在一个图片框上实现是很难完成的,所以设计双通道波形显示程序时,可在窗体上放置两个图片框,每个图片框用于显示一个通道的波形,编程时在两个图片框中交替显示一个通道的波形。当显示速度较快时,宏观上可得到双通道同时显示的效果。

5 有源时钟模块

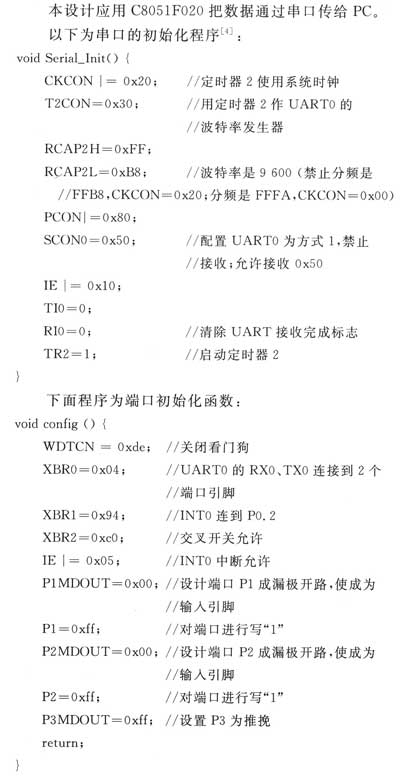

本设计ADC的采样率高达40 Msps,所以ADC的采样时钟用40 MHz有源晶振。有源时钟及分频电路如图4所示。

把40 MHz晶振分成不同的8个频率,这样可调节ADC的采样率,以适应不同的被测信号。这部分电路在做PCB时要注意走线,有源晶振和ADC之间距离不要超过1 000 mil(2.54 cm)。另外,做PCB时应把数字地和模拟地分开,最后用O Ω电阻跨上;最好两面"铺地",这样可以大大提高PCB的可靠性。

结 语

本设计的优点就是可以用较低的成本制作出性价比很高的示波器,能很好地满足学生或一些经费不是很充足的业余电子爱好者的需求。经过试验,整个系统非常稳定。测方波时,采样率最好是被测信号频率的5~8倍,这样效果能达到最佳。

本设计负责信号传输的CPU是C8051F020。C8051F系列单片机是完全集成混合信号的系统级芯片,具有与8051兼容的控制器内核,与MCS-51指令集兼容;除具有标准8051的数字外设部件外,片内还集成了数据采集和控制系统中常用的模拟部件和其他数字外设及功能部件。C8051F单片机采用流水线结构,机器周期由标准的12个系统时钟降为1个系统时钟周期,处理能力大大提高,峰值性能可达25 MIPS。

数字存储示波器 相关文章:

- 利用数字存储示波器测量特殊信号(11-02)

- 基于DSP的数字存储示波器的设计方案(03-23)

- 简易数字存储示波器中控制器模块的设计(01-12)

- 一种数字存储示波器智能触发技术研究(01-12)

- 数字存储示波器的产品特点(12-29)

- 数字存储示波器的工作原理(12-29)