基于直接数字合成技术的高速串行信号接收端容限测试新方法

编辑笔记:主要介绍串行信号的特性、传统数字信号源实现串行信号接收端容限测试的方法及其局限、直接合成信号源的实现方法及其优势,以及模拟信号源直接合成的方式在目前比较流行的串行标准中如SATA、Display Port、HDMI等的实际应用。

引言

在系统或者芯片的验证过程中,使用高速串行信号标准的芯片的接收端测试都需要激励信号源,一直以来,设计人员几乎完全依赖数字信号发生器,为串行测试生成二进制信号。他们在数字信号中运用输入信号的幅度调节、注入抖动、相位偏移调节等手段来进行比较恶劣的工作环境的模拟,以考验接收端的接收容限。但是,信号源领域中的新技术正在改变这一切,直接合成工具可以帮助设计人员创建现实程度更高的信号,并极大地减少复杂的测试设置和多种设备共用可能引入的测量误差。

直接数字合成方式产生信号的意义

串行信号完全由简单的二进制数1和0组成。为什么要使用直接数字合成模拟波形来表示数字数据呢?这是因为在数字信号中隐含的是模拟事件。书本上理想的数字信号的零上升时间和完美的"平顶"都是虚拟的,实际的工作环境具有噪声、串扰、反射、电源变化和其他缺点,每个缺点都会给信号带来影响。直接合成信号源的优点是能够完全"模仿"实际信号的模拟特点,可以任意控制信号的上升时间、脉冲形状、延迟、畸变、抖动变化规律等,这正是严格的串行总线测试所需的操作。泰克的AWG7000就是使用直接数字合成的方式产生信号的任意波形发生器,可以生成一个测试信号,拥有所需的全部时序、幅度和失真特点,而不是像一般的数字信号源那样先生成一个"干净"的理想信号,然后再通过各种组合去劣化信号来模拟真实环境。

实际工作环境中高速串行信号的模拟特性

由于传输介质的衰减以及反射会导致信号不同程度的劣化,具体表现为抖动的增大,信号幅度的衰减等。在实际工作环境中,随着信号速率的提高,传输介质对信号的影响越来越明显,信号一般会随信号速率和传输路径长度成比例劣化。在大规模的工程化生产制造过程中,可能会牺牲PCB、连接器、线缆的性能来换取成本的优势,这就更增加了接收端的容限要求。

由于时钟芯片的抖动影响,电源平面的波动干扰,以及串行信号周边低频但高能量的信号的串扰,这些都会导致串行信号发生时序上的变化,这种变化表现为信号边沿的抖动有规律的跟随着干扰信号的变化而变化;或者为了减少EMI的辐射,特意在时钟信号上叠加一个低频的调制,使信号的频率随着调制信号而有规律的升高或降低,频谱扩散在相对宽的频率范围内,而降低频谱的尖峰值,一般称为SSC(扩频时钟)。

为了减少传输介质的衰减而造成的波形的畸变和ISI的抖动成分的增加,提高传输过程中的信号完整性。业界普遍使用了去加重(de-emphasis)的技术,以补偿传输线对高频分量的衰减,改善接收机输入上的信号保真度。但必须在设计阶段全面评估串行设备对去加重的响应。在调试过程中可以根据实际的情况,调节去加重的比例以获得最好的传输效果。

传统数字信号源对串行信号特性进行模拟的方法

一般的数字信号源能够对比较单一的规律性变化的数字信号进行模拟,如信号中含有随机噪声,或者信号的抖动以单一的正弦规律或者三角波规律变化的情况。可以用多个仪器混合注入不同特性的抖动和噪声实现。但如果信号的劣化是不规则的或者以比较复杂的规律变化的,如在正弦抖动中含有电源或者其他高能量信号干扰引起的抖动,数字信号源就难以进行模拟了。

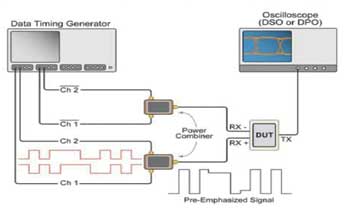

图1 数字信号源实现"去加重"特性信号的方法

对于串行信号标准中常用的"去加重"特性的实现,数字信号源则需要使用多通道以及Power Combiner电源组合器进行复杂的连接来实现,而且要精确控制多个通道的相位关系,否则得到的信号会与预期大相径庭,原理如图1所示,将CH1相对于CH2延迟一个比特位(UI),然后将两个通道相减,就可以得到图1去加重的信号。

使用直接数字合成原理的AWG(任意波形发生器)如何对串行信号进行模拟

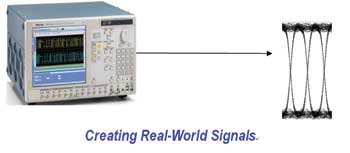

直接合成是一种基于采样的技术。直接合成信号源 (AWG)从样点中创建模拟波形,在带宽和采样率能达到的范围内,AWG存储器中的样点基本上可以定义任何波形,这些样点可以从示波器采集的实际波形中获得,也可以采用公式或者算法去任意定义。

图2 直接数字合成信号源对串行信号的模拟方法

直接合成信号源除了能够合成含任何抖动规律或者噪声的信号,建立随机抖动和确定性抖动的影响模型,以定量方式和定性方式改变施加的效应外,还能模拟信号在传输时由于特定介质的不同特性导致

- 频宽、取样速率及奈奎斯特定理(09-14)

- 为什么要进行信号调理?(09-30)

- IEEE802.16-2004 WiMAX物理层操作和测量(09-16)

- 为任意波形发生器增加价值(10-27)

- 基于PCI 总线的高速数据采集系统(09-30)

- 泰克全新VM6000视频测试仪助力数字电视等产品测试 (10-06)