低频数字相位(频率)测量的CPLD实现

设计的低频测相仪,满足以下的技术指标:a .频率20-20KHz;b .输入阻抗≥100KΩ;c.相位测量绝对误差≤1度; d.具有频率测量和数字显示功能;e.显示相位读数为0度--359度。

1系统工作原理

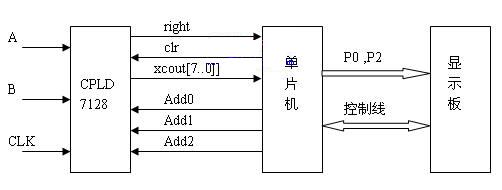

图1 测频测相系统原理框图

系统工作原理如图1所示,系统运行时,首先由单片机通过clr控制线送清零信号,启动CPLD的计数模块,在设计的CPLD内部控制模块作用下,记录AB两相的相差间隔时间内的标频个数(测相计数器),同时也记录下A相一个周期内的标频个数(测频计数器),此后测频和测相计数器处于保持状态,同时送出right信号表明完成测频测相的计数,单片机可以读数据。

单片机和CPLD的数据采用独立接口方式,这样设计比较灵活,可以不受单片机总线时序的影响。由ADD[0..2]进行控制,分别读取测频测相计数器中的19位数据,并存于单片机中,进行后续的计算。单片机完成数据的运算后,将所得数据转化为10进制,送到显示板进行显示。显示板共有8个数码管,其中,前5位用于显示频率(最大为20000Hz),后三位显示相位(最大为359度)。

在CPLD设计中,根据计算,选取测频、测相计数器长度均为19位,在标频信号为10MHz时,相位测量精度小于1度。若只用89C51,其自带的计数器只有16位,且不易同时实现测频测相的功能。故选用CPLD实现其测频测相的计数功能,并设计了独立的数据接口,以便与单片机交换数据[5、6]。

2 CPLD测频测相模块工作原理

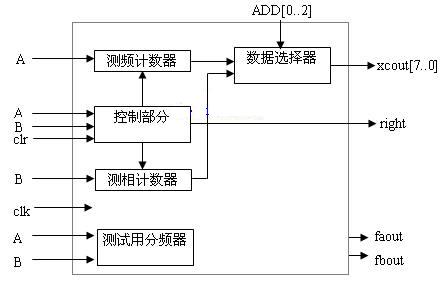

图2 CPLD测频测相内部原理框图

如图2所示,利用VHDL语言设计了完成测频测相计数功能的数字芯片。整个芯片由测频计数器、测相计数器、控制部分、数据选择器和测试用分频器5个部分组成。

控制部分主要是利用状态机原理,设计了检测一个测频周期的控制电路。在clr信号为高时,启动测频测相计数器,此时,状态机处于计数工作状态;当A相第一个上升沿到来时,测频测相计数器同时启动,开始计数;当B相第一个上升沿到来时,控制部分控制测相计数器停止计数;当A相第二个上升沿到来时,控制部分控制测频计数器停止计数,同时送出计数完成信号right;此后测频测相计数器处于保持状态。

单片机读数时,通过设置add[0..2]数据选择器的地址选通端,依次送出测频计数器中的19位数据,8位一组,从xcout[0..7]端口送出,单片机需分3次读完测频计数器中的19位数据,数据选通端设置为001,010,011;同理,单片机也需分3次读完测相计数器中的19位数据,数据选通端设置为100,101,110。

为了测试方便,设计了测试用分频器,该分频器系数可以在VHDL源程序中改动,如为1000,则将测试时用的标频信号10M进行1000分频,分频后频率为10KHz,正好处于20-20KHz范围内。

3 单片机程序

如图3所示,系统上电后,首先由单片机送出清零信号,启动CPLD中的测频测相计数器,CPLD进行测频测相的计数,单片机查询到right=1,则表明计数器完成计数工作,开始读取CPLD中的数据。否则,就等待。单片机通过控制CPLD中数据选择器的地址选通端add[0..7],分别读取测频、测相计数器的19位数据,并进行相应的计算。计算中首先调用频率计算子程序,计算出相应的频率,然后再调用相位计算子程序,计算出相应的相位,再调用进制转换程序,将16进制的数转换成10进制,最后调用显示子程需,在8位数码管中显示出测量的频率、相位值。由于篇幅关系,此处不再详述具体程序和显示部分的设计。

4 结束语

由单片机晶振产生的6M信号,经过一个与非门整形为矩形脉冲,再经过CPLD7128的内部设计的分频器分频(分频系数为1000、2000、3000、4000),由该系统进行测频测相。AB二相的信号加上一个反相器,则从理论上讲,相位相差180度。实际测量结果为,频率分别是6000、3000、2000、1500Hz,相位为180度,与理论完全符合。利用DDS数字移相信号发生器产生不同频率和相位差的信号实测证实,该系统指标符合设计要求。随着EDA(电子设计自动化)技术和微电子技术的进步,CPLD的时钟延迟可达到 级,结合其并行工作方式,在超高速、实时测控方面有非常广阔的应用前景;并且CPLD&FPGA具有高集成度、高可靠性,几乎可将整个设计系统下载于同一芯片中

- 以频域时钟抖动分析加快设计验证流程(01-22)

- 基于PLL技术的合成频率源设计(11-13)

- 选择你的PLL锁定时间测量(06-07)

- 如何实现功率测量的“神同步”?(06-23)

- 同步源和PLL源在功率分析仪中的作用(06-09)

- 一种准确地预测由泄漏电流引起的PLL基准杂散噪声之简单方法(上)(04-01)