用串行RapidIO交换处理高速电路板设计的信号完整性问题

信号完整性(SI)问题正成为数字硬件设计人员越来越关注的问题。由于无线基站、无线网络控制器、有线网络基础架构及军用航空电子系统中数据速率带宽增加,电路板的设计变得日益复杂。

目前,芯片间高速串行链接已经获得广泛应用,以提高整体吞吐性能。处理器、FPGA及数字信号处理器可相互传输大量数据。此外,该数据可能必须从电路板发出,通过背板传输至交换卡,而交换卡可将数据发送至机箱内的其他卡或"系统"内的其他地方。支持RapidIO|0">RapidIO的交换可实现这些不同组件之间的互连,并广泛用于满足这些应用的实时带宽需求。

本文主要探讨涉及高速接口设计(RapidIO交换的主要功能支持这些高速接口设计)的信号完整性难题以及其他相关事项,优化RapidIO交换的功能旨在实现高速设计中较高的信号完整性。

高速接口设计难题

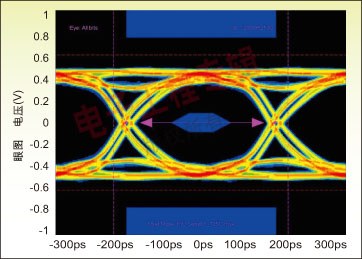

信号质量对于系统的各个方面均非常重要。对于串行RapidIO而言,信号质量通过接收眼图的大小进行量化。接收眼图是一个无限延续的轨迹,其中,波形会随上一个轨迹不断重复(如图 1 所示)。眼图开得越大,信号质量就越好。

信号质量可能受多方面的影响:信号通道中出现噪声或其他杂乱信号、信号通道布线差、外部源的传导或辐射、系统本身产生的噪声。上述所有因素结合在一起会导致接收眼图缩小。除电路板级问题外,信号完整性亦可能受到连接的源(传输端)及目的地(接收端)的影响。因此,应在整体系统级的信号完整性中考虑源及目的地的IC特点。

电路板级设计的考虑因素

就电路板设计而言,应考虑的常见因素包括:

1. 电路板的电源输入、本地调节器的输出及分配

2. 时钟生成及分配

3. 退耦

4. PCB基础材料

5. 芯片间连接

6. 电路板间连接及背板连接

7. 电路板层叠及阻抗控制

8. 机架间连接器、电缆及接头

图 1:典型高速信号眼图。

工作频率高于300MHz时,适用于较低频率电路板设计的大部分设计最佳惯例均需修改。必须考虑当波长与电路板尺寸可比时出现的因素。这不仅适用于基本频率的波长,也适用于构成完整波形的傅立叶(频域)分量。

FR4材料仍可成功用作电路板的基础材料,但在较高频率下,不仅需要考虑材料的介电常数,还需要考虑损耗系数。过孔的设计也变得非常重要,因为未使用的管长部分(在较低频率下其影响可以忽略)的阻抗会与较厚电路板及背板的阻抗不匹配。最好完成设计后仿真,以引起对信号完整性不太理想的布线的注意,并指出串扰区域。

电路板上信号完整性方面的特定难题是由于高速处理器总线及高速内存接口的存在、时钟生成及时钟噪音以及各种电路板噪音源而引起,通常包括:单端并联总线、电源分配、阻抗匹配、接地弹跳、串音及时钟生成。

串行RapidIO交换机

串行RapidIO互连可用于处理以上所讨论的一些信号完整性难题。RapidIO是芯片间、电路板间及机箱间互连的一个成熟、开放标准,由嵌入式计算领域领导厂商设计,可满足在无线基础架构、网络、存储、科学、军事及工业类市场中设备对可靠性、成本效益、性能及可扩展性的要求。

RapidIO是一个专为满足当前及未来嵌入式应用需求而设计的点到点数据包交换互连协议。RapidIO物理层1x/4x链接串行规范可满足使用电子串行连接的设备的物理层媒介要求。该规范定义了使用单向差分信号的设备之间的全双工串行物理层接口(链接)。此外,对于需要更高链接性能的应用,它还允许将四个串行链接组合在一起。它还定义了用于链接管理及通过链接传输数据包的协议。

RapidIO系统的架构由端点元件及连接端点的交换结构组成。设想端点作为邮件系统中的出发点,交换机作为截取包裹并将包裹发送至目的地的邮局。RapidIO互连架构根据规范被划分为层状架构,包括逻辑层、公共传输层及物理层。RapidIO协议的物理层由芯片串行器-解串器(SerDes)处理。SerDes的特性对硬件设计人员在设计电路板时所面临的信号完整性问题有一定的影响。交换机设计的许多其他方面也将影响信号完整性。

RapidIO 交换的特性简化电路板设计并实现较高的信号完整性

时钟生成

就启动器而言,sRIO交换机必须具有实现低抖动的无噪时钟信号。低抖动信号基本上具备低相位噪音的特性。若增加输入时钟信号以实现较高频率的输出信号,则必须优化芯片电路,以产生最小的相位噪音。Tundra的Tsi57x串行RapdIO交换机通过采用集成低噪音放大PLL的125MHz及155MHz时钟产生高达3.125Ghz的输出信号。许多产品采用独立电路实现上述功能,因而无法像Tundra交换芯