基于DDS技术的声纳信号模拟器

的统一。它具有相位变换连续、频率转换速度快、频率分辨率极高、相位噪声低、易于用微机等多种方法控制以及体积孝集成度高等多种优点,因而近年来DDS在理论和应用上得到飞速的发展。

DDS的基本结构如图2所示。

由于DDS具有频率和相位可以确定数控的特点,因而将DDS器件作为成像声纳信号模拟器的关键部件,并辅以相应的控制和接口逻辑等,就可以实现对任意方位和距离目标回波的精确模拟。

2.2 DDS构成的模拟器结构

基于DDS技术的成像声纳信号模拟器的结构如图3所示。

模拟器共有48个信号通道,每个通道模拟声纳接收基阵中一个基元的输出。通道电路由单片DDS器件AD9830及其接口逻辑电路、输出I-V变换器及滤波和跟随电路构成。各个通道的DDS器件与CPLD之间的接口采用16bit位宽的并行总线。

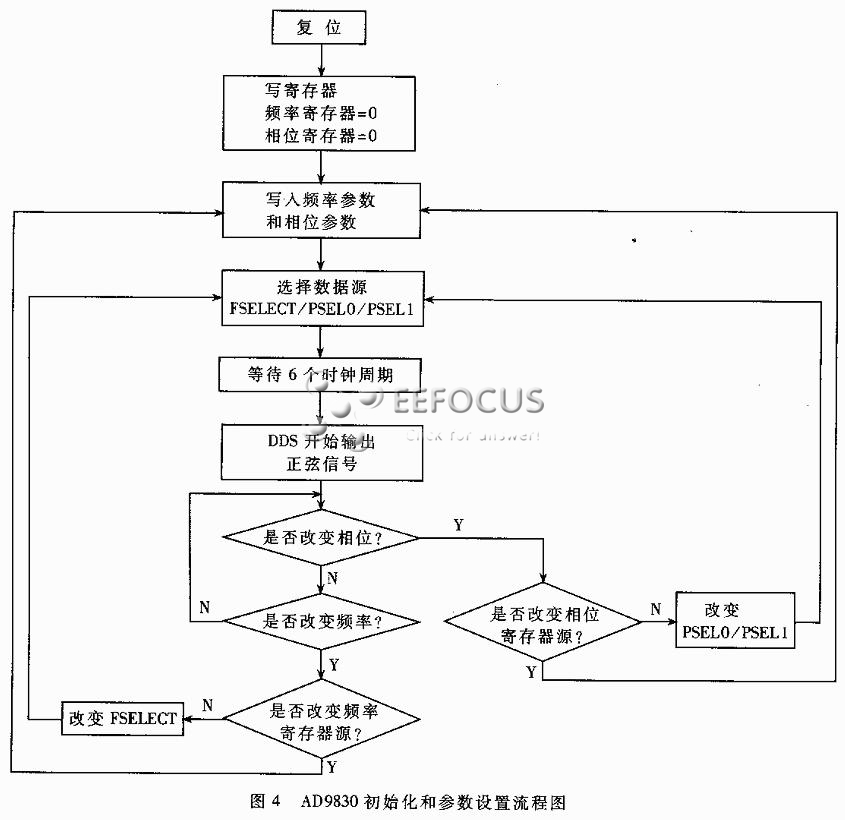

用户将要模拟的目标方位、距离、信号幅值等信息输入到主机的应用程序界面中,应用程序根据这些信息,按照近场聚焦的算法计算出每个通道信号相对于参考通道的相位差等参数,然后通过RS-232串行总线将这些参数下传到信号模拟器中。信号模拟器中的微控制器将这些参数接收并解码,并将每个通道信号的频率和相位等参数通过CPLD写入相应通道的DDS器件的控制寄存器中。AD9830初始化和参数设置的流程图见图4。

2.3 目标距离的模拟

信号模拟器从主机接收到的参数除了各通道频率和相位差外,还包括输出信号的幅度(增益)控制曲线参数。幅度控制参数也由单片机解码并按照曲线的定时参数发送到DAC中,数模转换后的幅度控制信号送入AD9830的Rset端,从而控制了输出信号的幅度。

这个幅度控制电路是一个开环系统,具有较好的动态性能,带宽可达100kHz。采用适当幅度(增益)控制曲线并配合外部触发源,可以实现对预定距离上点目标回波信号的模拟。其工作原理如图5所示。要模拟与接收基阵相距分别为L1和L2的两个点目标,则按照模拟器中DAC的转换速率生成相应的幅度控制曲线。该幅度控制曲线在模拟器中与外部触发信号同步,而外部触发信号与成像声纳发射机同步,即它的上升测对准声纳发射脉冲的前沿时刻。这样在幅度曲线的控制下就可以精确模拟预定距离上的点目标回波。

本文采用的DDS器件AD9830中共有4个相位寄存器,如果事先写入计算好的相位参数,并且在使用幅度曲线控制的同时配合相应的相位转换,就可以在一次发射回波中模拟最多4个不同方位和距离上的点目标。

3 几个注意事项

3.1 参考时钟的扇出(Fan-out)

为了提高系统的可靠性和可扩展能力,整个模拟器采用了3U EuroCard机箱+背板+插板的结构,每8个通道电路在一块插板上实现,总线接口和参考时钟等信号位于背板。这样的结构造成参考时钟的布线拓扑比较复杂。并且因通道数较多,所有通道的DDS器件公用一个参考时钟,时钟扇出和布线以及阻抗匹配等就显得非常重要。如果扇出不合理,造成各通道DDS输入端的参考时钟存在延迟,就会影响系统的精度。另外由于参考时钟频率高达50MHz,信号完整性问题也将影响系统的正常工作。

本文采用了Cypress公司的高速时钟分布器件CY2308,将石英晶体振荡器产生的参考时钟扇出为6个独立的时钟,分别送到6块通道板,严格保证每条时钟信号在PCB上的路径等长并进行精确的阻抗匹配。同时,每块通道板中也使用同样的扇出和布线方法。这样,各个通道的时钟间延迟小于200ps,可以保证模拟器的精度。

3.2 混合电路的布线

由于信号模拟器中既存在大量高频数字逻辑控制信号,输出信号又是多通道微弱模拟信号(mV级),因而要特别注意数模混合电路的避布线、退耦、电源和地平面的分割等事项。这方面有许多专著讨论,本文不再详述。值得注意的是,DDSLayout应严格按照参考设计进行,以确保系统的性能。

3.3 DDS器件的安全

单片集成式DDS器件多数采用CMOS|0">CMOS工艺生产,比较脆弱易损,在设计与调试中应特别注意。由于信号模拟器在使用中可能出现输出补意外短路等情况,因此在输出级采用跟随器以避免DDS意外损坏。此外,在设计幅度控制电路时应留有一定余量,避免DDS因输出电流过大而失效。

本文提出并实现了采用DDS技术的新型声纳信号模拟器。完成的模拟器样机克服了传统模拟技术结构复杂、可靠性差、可调范围窄等弊端,可以实现对任意方位和距离上点目标回波信号的精确模拟,使用方便可靠,在某高频成像声纳的设计和调试中起到了十分关键的作用。同时,该模拟器具有较好的适应性和扩展能力,可以用于未来的多种型号成像声纳的调试,具有很强的工程实用价值和广阔的应用前景。<script event="onload" for="window"

- DDS函数信号发生器的优点(09-28)

- 基于DSP与AD9852的任意信号发生器 (11-03)

- 基于DSP Builder的DDS设计及其FPGA实现(11-03)

- 基于AD9858的线性调频源设计(11-03)

- 基于DDS的高分辨率信号发生器的实现(11-04)

- 基于FPGA的DDS调频信号的研究与实现 (11-04)