用创新的技术找出混合信号设计中的问题

找出死锁问题的根本原因

安捷伦科技的工程团队最近在设计一块新的数据采集电路板(acquisition board)时,遭遇到一个难缠的问题,这块板子平时可以正常运作,但偶而却会死机。团队人员利用Windows debugger确定了造成死锁(lock-up)的原因是:有一个 "配置写入"周期有时候无法收到确认信号。他们修改固化软件,重复"配置写入",将死锁情形的出现频率由每隔几小时提高到每隔几分钟出现

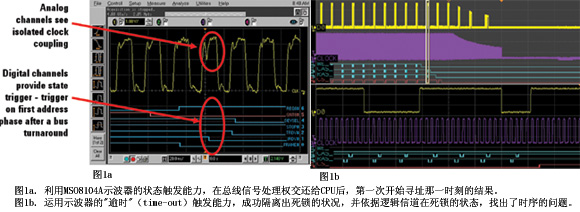

一次。图1a显示了利用MSO8104A示波器的状态触发能力,在总线信号处理权交还给CPU后,第一次开始寻址那一时刻的结果。由图中可以看出与时钟信号有关的一个异常的电压跌落,这是因相邻地址线的电容耦合所造成的。在图1b中可以看出,在较长的时基范围下检视这些信号,当电路进入死锁的状态时,系统中一些周期性出现的信号会停止改变状态, ,设计团队运用示波器的"逾时"(time-out)触发能力,成功隔离出死锁的状况,并依据逻辑信道在死锁的状态,找出了时序的问题。

一次。图1a显示了利用MSO8104A示波器的状态触发能力,在总线信号处理权交还给CPU后,第一次开始寻址那一时刻的结果。由图中可以看出与时钟信号有关的一个异常的电压跌落,这是因相邻地址线的电容耦合所造成的。在图1b中可以看出,在较长的时基范围下检视这些信号,当电路进入死锁的状态时,系统中一些周期性出现的信号会停止改变状态, ,设计团队运用示波器的"逾时"(time-out)触发能力,成功隔离出死锁的状况,并依据逻辑信道在死锁的状态,找出了时序的问题。

重要事件的出现频率

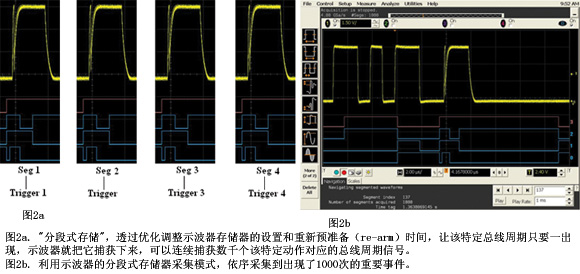

在图1a所示的例子中,出现系统死锁情形的概率/频率非常低--大约每2到8小时才出现一次。此处需要设想的问题是:如果工程师无法利用debugger将问题复制出来怎么办?我们要如何确定该问题与"配置写入"周期之外的其它总线周期无关呢?所幸,安捷伦科技的MSO8000系列示波器提供了一个称为"分段式存储"(segmented memory)的先进功能,可透过优化调整示波器存储器的设置和重新预准备(re-arm)时间,让该特定总线周期只要一出现,示波器就把它捕获下来,可以连续捕获数千个该特定动作对应的总线周期信号,图2a显示的就是一个例子。

MSO混合信号示波器的模拟信道和数字信道的采集存储器可被分为许多段,当示波器的触发条件第一次出现的时候,波形数据会被填入第一段的存储器,当触发条件第二次出现时,则会填入第二段的存储器,依此类推。在图2b显示的例子中,利用示波器的分段式存储器采集模式,依序采集到出现了1000次的重要事件。事实上,利用MSO8000的采集存储器(示波器通道选件深达128 M,逻辑信道是标配,每信道32M)最多可以采集32,000段的波形。在采集到指定的区段数之后,可以使用荧屏右下方的浏览控制键,轻易地逐一回放每个区段,以便清楚地查看信号异常是否只与示波器的逻辑信道所采集到的一个重要时序事件有关,或是DUT还有其它关键的总线动作也会造成信号异常的现象?分段式存储器采集模式同时支持示波器信道和逻辑信道,对内嵌式系统设计的除错有很大的帮助,因为这种设计大多是以状态机(state machine)为主,您可以透过逻辑信道来设定触发条件,观察每一个状态的信号行为。

浏览控制功能不仅在使用分段式存储器采集模式时可以使用,而且在串行总线译码模式下也可以使用。图3所示为I2C总线的信号,与译码窗口内的信号是时间相互关联的。虽然I2C不是一种高速的串行总线,而且就这种低速总线的时钟与数据信号而言,信号完整性的问题可能也不是主要的考虑点,但是利用这种通讯信号进行触发,并且让示波器同步进行采集,或许可以揭露出系统中其它时间相互关联之模拟和/或高速数字信号的信号完整性问题。在某些情况下,我们可能会知道待测信号或许会出现问题,但却不知道何时会发生问题,或是问题跟哪个信号有关。在串行总线译码功能的协助下,示波器可以显示出图3a中的情形:只有当一个特定的I2C读取动作发生时,才会出现一个双周期的雷达chirp输出信号。您可以浏览译码列表窗口中的每一个读取动作,以验证该特定的事件(其它相关信号)是否有发生。这个概念与FPGA的除错方式很类似,安捷伦科技的MSO8000支持Xilinx FPGA内部节点自动切换和测试,可以将FPGA内部节点(> 1000个多个待切换测试的节点)与外部信号的时间相互关联来显示和分析。一旦工程师知道这些问题何时会发生,以及问题与哪个信号和/或总线周期相关联之后,通常就可以快速地解决设计的问题。

- 新型便携式泰克示波器方便了电子工程师(08-23)

- Tektronix推出数字储存示波器,频宽达200MHz (08-24)

- 安捷伦推出的Infiniium 8000 系列示波器(08-23)

- 用示波器测量确定性抖动(08-25)

- 如何用函数信号发生器产生低占空比的信号(08-23)

- 抖动测量三种方法(08-25)