基于TI达芬奇技术的高速网络摄像机设计方案

多媒体技术和网络与移动通信的飞速发展激发了人们进行视频信息交流的需求。随着视频监控系统逐步向数字化发展.开发新一代基于计算机网络以及多媒体压缩算法的视频监控系统成为行业的主流方向。然而随着视频应用的迅速增加,开发者往往需要花费很多时间来熟悉各种多媒体的标准,最终只能通过编写与改进代码来进行开发与改变。随着美国TI公司推出达芬奇(DaVinci)平台后,这一切都在发生改变。

1 达芬奇技术的主要特点

达芬奇平台是典型的基于共享存储的嵌入式多处理(ARM,DSP,VICP,视频前端和后端等)环境,支持的关键技术是片内实现了多通道的交换中心资源(Switch Central Resources,SCR)。基于片内SCR,达芬奇平台在片内多处理器之间形成了典型的C/S架构:计算能力强大的DSP可以作为服务器提供算法的实时计算服务;带有JAVA处理能力的ARM9实现网络,硬盘音视频I/O等用户界面。美国TI公司在达芬奇平台上专门为音视频编解码(Codec)多媒体应用精心设计了系统框架,提供了丰富的系统程序接口SPI,应用程序接口API以及视频,图像,话音和音频千余种流媒体算法组件。他们与操作系统,中间件构成了一个应用系统的大部分内容,应用系统开发团队只需要将他们封装成运行包,就能得到高可用性和高可靠性的产品。

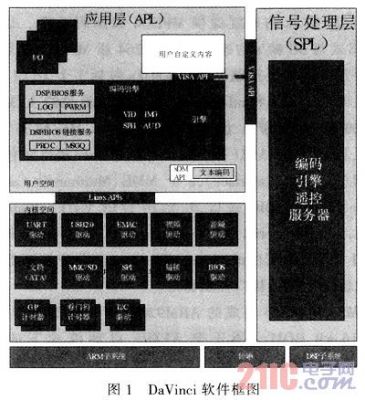

达芬奇平台的最大特点就是基于DSP与ARM的SOC芯片,和与之相关的相关软件,如图1所示。

对达芬奇平台,硬件上给与双核架构强有力的支持,在DSP端用DPS/BIOS来支持音/视频算法的运行,在ARM端用MontaVistaLinux(MV)来支持其对外设的管理。对于ARM与DSP之间的数据交叉,则用Codec Engine和Codec Server来加以管理。达芬奇平台的先进性,对高端音/视频系统来说,无疑是开发平台的最好选择。

2 TMS320DM365介绍

TI公司的TMS320DM365是一款面向多媒体技术应用的高性能芯片。TM320DM365功能框图如图2所示。

内核方面TMS320DM365集成ARM926EJ-S.H.264协处理器(HDVICP),MPEG4/JPEG协处理器(MJCP),能以1080p格式与10帧/s的速度提供H.264编解码功能,和以1080p格式与24帧/s的速度提供MPEG4编解码功能,以及以720p格式与30帧/s的速度提供H.264或MPEG4编解码功能。存储方面扩展存储器接口EMIFs包括1个16位256 M地址空间的DDR2和mDDR,以及1个16/8位的AEMIF,可扩展的类型有8/16位NAND Flash,16Mb NOR Flash,SRAM,16位OneNAND等。其他外围扩展控制器还包括16位HPI(Host-Port Interface),2个MMC(Multimedia Card)/SD(Secure Digital)/SDIO接口,1个16位的WDT(Watch DogTimer),5个SPI(Serial Port Interface)接口其中每个具有两个片选,1个主/从I2C(Inter-Integrated Circuit)总线控制器,1个支持2.0USB OTG接口控制器等。

TMS320DM365集成的ARM926EJ-S处理器包括32 kBRAM、16 kB ROM(用于非AEMIF启动模式下的ARMbootloader)、16 kB指令缓存、8 kB数据缓存、CP15及MMU等。其中CP15用来对指令、数据缓存、MMU以及其他ARM子系统进行配置及控制。MMU使用统一的TLB来对页表中存储的信息进行缓存,并为类似Linux、WindowsCE、ultron以及ThreadX等操作系统提供虚拟内存。该处理器的写缓冲数据容量高达17 kB,使其可以大幅提高内核的性能。

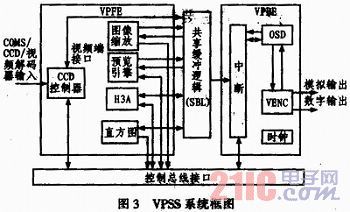

TMS320DM365中的视频处理子系统(VPSS)由两个接口,分别用于视频捕获的视频前段(VPFE)输入接口和用于图像显示的视频后端(VPBE)输出接口。图3为视频处理子系统系统框图。

VPFE模块主要用于捕获视频信号,也可以直接从前端输入已有的视频信号。VPFE输入接口有1个CCD控制器(CCDC)、1个预处理器、柱状模块、自动曝光/白平衡/聚焦模块(H3A)和寄存器组成。CCDC可以与视频解码器、CMOS传感器或电荷耦合装置连接;预处理器是一个实时的图像处理器,它把来自CMOS或CCD的原始图像从RGB转变为YUV422的编码;柱状模块和H3A模块实现基于原始图像信息的硬件操作。

VPBE输出接口由1个OSD引擎和1个视频编码器组成。OSD引擎能够显示两组独立的视频窗口或两组独立的OSD窗口,还可以以2个视频窗口、1个OSD窗口和一个属性窗口的形式显示。OSD用于在视频图像上叠加音量,图标等位图或图像信息。视频编码模块提供数字输出和模拟输出。数字输出支持24bitRGB888格式、8/16bit BT.656以及具有独立的水平和垂直同步功能的CCIT.601输出;模拟输出支持4路10bit DAC,均工作于54 MHz,支持复合NTSC/PAL、S端子和分量视频。

3 系统硬件设计

系统硬件结构如图4所示,本系统选择以TMS320DM365为嵌入式处理器,外围电路包括有音频、视频信号

- CCD摄像机最低照度浅析 (05-11)

- 基于TMS320DM270平台的数码摄像机的设计与实现(02-25)

- 基于FIC8120和PoE的IP-Camera设计(03-11)

- 解析智能视频监控系统的构建以及应用(05-14)

- 如何应对高清移动多媒体设计中的挑战?(09-18)

- 无线摄像头的应用(10-19)