基于FPGA NiosII的MPEG-4视频播放器设计

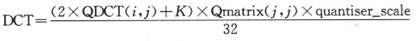

DCT表示反量化后的AC系数,那么AC系数的IQ变换公式如下:

式中,quantiser_scale为0~112之间的两组数值,分别对应不同的比特流控制状态。但是在本系统采用的XviDCodec版本中,比特流控制功能并没有得到实现,所以这里quantiser_scale的取值固定。

反量化得到的结果通过饱和化,使其限制在[-2048,+2047]之间。

IQ在FPGA上按照图3的框图进行硬件实现。

2.1.2 反离散余弦变换

IDCT是DCT的逆过程,用于还原DCT系数矩阵。

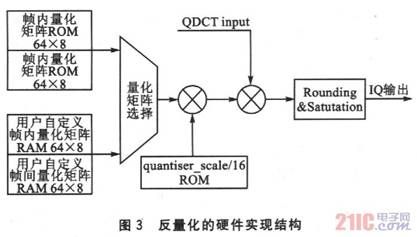

IDCT过程可由下面的公式描述:

将8元的输入向量[X0,X1,X2,X3,X4,X5,X6,X7]分成奇元素[X1,X3,X5,X7]和偶元素[Xo,X2,X4,X6],8×8矩阵则用2个4×4矩阵来代替,奇元素和偶元素分别与这2个矩阵v和u相乘,生成2个4×4向量p和q,通过加减向量p和q,可得到输出向量x。

算法可以表示成下面的公式:

基于8×8矩阵的IDCT算法,在FPGA上按照图4所示的结构加以硬件实现。

2.1.3 运动补偿

运动补偿是一种大量、单调的运算。为了能实现运动补偿,采用了多级、多个运算单元并行流水运算的方式,如图5所示。

运动补偿模块的控制很复杂。实际设计时将它分成几个子模块:补偿控制、补偿地址产生、差分数据提供以及补偿运算。这几个子模块直接采用硬件逻辑设计,运行时无需NiosII处理器干预。其中补偿控制是完成整个运动补偿的控制,提供输入控制信号、输出控制信号、缓存控制信号、预测数据和差分数据等;补偿地址产生用于生成预测数据在帧缓存中的地址及补偿结果的写地址;差分数据负责接收IDCT的结果,通过缓存在适当时机提供补偿使用;补偿运算则完成最终预测数据的计算。

2.1.4 YUV-RGB转换

根据YUV到RGB色彩空间的转换关系,对每个乘积项都预先做出结果,存放在ROM当中。对每一个YUV分量的输入,由硬件逻辑产生存取地址,并进行加法运算,从而得到对应的结果。其实现结构如图6所示。

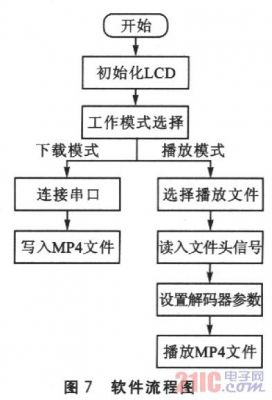

2.2 系统软件工作流程

本系统的软件工作流程如图7所示。

结 语

该系统采用基于Altera FPGA嵌入式NiosII软核的SOPC平台实现,具有较低的硬件成本,IP核的大量使用,良好的系统扩展性的特点。

FPGA NiosII MPEG-4 视频播放器 相关文章:

- 利用FPGA和新技术,使LCD进入HDTV市场(08-27)

- 基于DSP和FPGA的电视观瞄系统设计(09-02)

- FPGA与SRAM相结合完成大容量数据存储(09-03)

- HDTV接收机中Viterbi译码器的FPGA实现(09-09)

- 基于FPGA的液晶显示接口设计 (09-26)

- 解决硬盘驱动器能耗难题(10-13)