测试3G手机的DigRF技术

时间:06-19

来源:21IC

点击:

DigRF准备替换RF与基带半导体器件之间的两种主要形式的数据通信路径:模拟信令,以及针对具体设计的私有数字信令(并行或串行)。MIPI(移动业处理器接口)联盟正在致力于采用DigRF(数字射频)标准,用一种基于分组的公共数字串行接口代替各种类型的I/Q(同相位/正交相位)信令接口。一个MIPI联盟工作小组已开发了用于2.5G和3G手机标准的DigRF规范,预计其后版本会增加支持4G标准的数据流量。

使用DigRF这种标准接口可以使设计者在元件选择时有更多的灵活性。例如,一名设计者可能准备从某家供应商采购一种高价的基带IC(可能是手机中最贵的芯片之一),而从其它供应商处购买RF、电源管理和其它器件。然而,DigRF技术在促成通用产品的极端灵活性时也带来了挑战,会影响到你的测试策略。

在RF接收测试期间,测试工程师的主要目标还与DigRF以前相同,即捕获I/Q信息,对获得的数据集执行定制的数字信号处理算法,并记录参数化结果,以确定设备是否合格。但与前代RFIC相比较,DigRF器件可能给生产测试增加大量开销。寻找尽可能减少这种开销的方式,就成为工程师在设计自动化生产测试系统时所面临的主要挑战。

理解接口

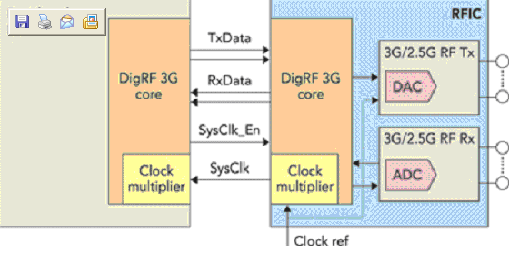

DigRF 3G定义了实现接口所需要的最小信号数;一个基本的手机配置只需要6根线(图1)。RxData/TxData信号在一个分组协议中传送I/Q数据以及控制与状态消息的数字表示。

图1. 基本的DigRF手机配置只需要6根线。

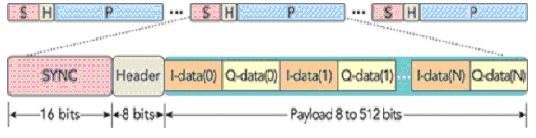

以DigRF信号传输的数据被封装在协议包或称帧内。每个帧都包括三部分:同步(sync),头(header),与有效载荷(payload)(图2)。每个包的开始都有相同的16 bit同步序列,数字接收电路用它对每个帧做实时选通相位的对准。

接下来的8个位是头,它定义有效载荷的作用与内容。头本身由三部分构成:3位表示有效载荷的大小,4位描述LCT(逻辑信道类型),1位表示CTS(清除发送)信号。

图 2. DigRF 3G数据帧开始于一个16 bit同步序列,后面是一个8 bit头和I、Q数据。

不同数据包的有效载荷部分有大小变化,从而产生不同级别的编码开销。LCT定义了有效载荷中包含的内容,以及可分类为控制数据或I/Q数据的内容。CTS允许在RF发射期间,由RF设备控制来自基带的数据流。

帧中余下的N位就包含了要传输的实际数据。例如,在DigRF 3G的非分集模式下,RxData帧将使用数据信道C和256 bit有效载荷,包含8 bit的交替I数据和Q数据。

DigRF 3G支持数字传输下的三种时序模式,具体取决于被传输RF信息的类型(表1)。DigRF标准还支持三种公共的输入基准时钟频率(19.0 MHz、26.0 MHz和38.4 MHz);时钟通过SysClk信号送至基带。与速度模式无关,DigRF处理器会用一个本地的FIFO缓冲管理数据流,当传输帧时会产生一个无法预测的时序。

生产测试的挑战

对采用DigRF协议器件作成功测试的关键是要找到一种方式,能在RF接收测试期间管控RxData包的不确定性状态。在对DigRF产品作RF接收测试期间,能观察到RxData信号合成状态的多级不确定性:

•相位时序;

•帧时序;

•帧类型;

•有效载荷中的数据。

312 Mbps的数据速率来自于一个1248 MHz主时钟(一般由PLL生成)的1/4分频器。在生产性测试系统中,考虑到影响RF前端的相位噪声性能的重要性,器件的时钟输入应由RF仪器提供。与普通数字子系统相比较,这个时钟源的起始相位通常是不可控的。DUT(待测设备)的输入时钟相位未定,PLL倍频器/分频器产生的相位也不确定,两者结合导致RxData输出时序无法预测,包括器件各上电循环之间,以及多地点并行测试配置中的不同器件之间的输出时序。

一种生产型测试仪应有这种能力,即在各次测试间对测试仪硬件和DUT作必要修改时,仍保持数字子系统的运行。它使测试仪能够维持相对于DUT输出的选通时序,避免在正式运行中的选通相位重调,节省了测试时间。

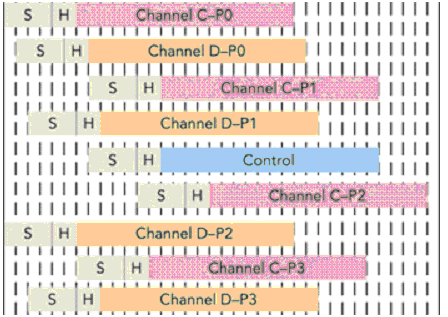

下一个重要的测试挑战是寻找一个能处理多级不确定性数据包传输性能的方式。如图3所示,在DUT的每个RF接收测试期间,测试仪都不知道每个包会在哪个测试循环中传输,包的类型会是什么,或者包的类型是否符合预期(例如,RFIC会生成一个主动的控制状态消息)。

图 3. 由于数据包的不确定性,在一款器件的每次RF接收测试期间,测试仪不知道每个包会在哪个测试循环中传输,包的类型是什么,或者包的类型是否符合预期。

马上能看出,测试程序不能在数字测试模式中采用固定循环周期的选通隔离所需I/Q数据。同样,对同步或头的数字匹配回路不能以DigRF速度,足够快地通过ATE仪器的流水线,仪器也不能完成对头信息的实时识别和决策。

使用DigRF这种标准接口可以使设计者在元件选择时有更多的灵活性。例如,一名设计者可能准备从某家供应商采购一种高价的基带IC(可能是手机中最贵的芯片之一),而从其它供应商处购买RF、电源管理和其它器件。然而,DigRF技术在促成通用产品的极端灵活性时也带来了挑战,会影响到你的测试策略。

在RF接收测试期间,测试工程师的主要目标还与DigRF以前相同,即捕获I/Q信息,对获得的数据集执行定制的数字信号处理算法,并记录参数化结果,以确定设备是否合格。但与前代RFIC相比较,DigRF器件可能给生产测试增加大量开销。寻找尽可能减少这种开销的方式,就成为工程师在设计自动化生产测试系统时所面临的主要挑战。

理解接口

DigRF 3G定义了实现接口所需要的最小信号数;一个基本的手机配置只需要6根线(图1)。RxData/TxData信号在一个分组协议中传送I/Q数据以及控制与状态消息的数字表示。

图1. 基本的DigRF手机配置只需要6根线。

以DigRF信号传输的数据被封装在协议包或称帧内。每个帧都包括三部分:同步(sync),头(header),与有效载荷(payload)(图2)。每个包的开始都有相同的16 bit同步序列,数字接收电路用它对每个帧做实时选通相位的对准。

接下来的8个位是头,它定义有效载荷的作用与内容。头本身由三部分构成:3位表示有效载荷的大小,4位描述LCT(逻辑信道类型),1位表示CTS(清除发送)信号。

图 2. DigRF 3G数据帧开始于一个16 bit同步序列,后面是一个8 bit头和I、Q数据。

不同数据包的有效载荷部分有大小变化,从而产生不同级别的编码开销。LCT定义了有效载荷中包含的内容,以及可分类为控制数据或I/Q数据的内容。CTS允许在RF发射期间,由RF设备控制来自基带的数据流。

帧中余下的N位就包含了要传输的实际数据。例如,在DigRF 3G的非分集模式下,RxData帧将使用数据信道C和256 bit有效载荷,包含8 bit的交替I数据和Q数据。

DigRF 3G支持数字传输下的三种时序模式,具体取决于被传输RF信息的类型(表1)。DigRF标准还支持三种公共的输入基准时钟频率(19.0 MHz、26.0 MHz和38.4 MHz);时钟通过SysClk信号送至基带。与速度模式无关,DigRF处理器会用一个本地的FIFO缓冲管理数据流,当传输帧时会产生一个无法预测的时序。

生产测试的挑战

对采用DigRF协议器件作成功测试的关键是要找到一种方式,能在RF接收测试期间管控RxData包的不确定性状态。在对DigRF产品作RF接收测试期间,能观察到RxData信号合成状态的多级不确定性:

•相位时序;

•帧时序;

•帧类型;

•有效载荷中的数据。

312 Mbps的数据速率来自于一个1248 MHz主时钟(一般由PLL生成)的1/4分频器。在生产性测试系统中,考虑到影响RF前端的相位噪声性能的重要性,器件的时钟输入应由RF仪器提供。与普通数字子系统相比较,这个时钟源的起始相位通常是不可控的。DUT(待测设备)的输入时钟相位未定,PLL倍频器/分频器产生的相位也不确定,两者结合导致RxData输出时序无法预测,包括器件各上电循环之间,以及多地点并行测试配置中的不同器件之间的输出时序。

一种生产型测试仪应有这种能力,即在各次测试间对测试仪硬件和DUT作必要修改时,仍保持数字子系统的运行。它使测试仪能够维持相对于DUT输出的选通时序,避免在正式运行中的选通相位重调,节省了测试时间。

下一个重要的测试挑战是寻找一个能处理多级不确定性数据包传输性能的方式。如图3所示,在DUT的每个RF接收测试期间,测试仪都不知道每个包会在哪个测试循环中传输,包的类型会是什么,或者包的类型是否符合预期(例如,RFIC会生成一个主动的控制状态消息)。

图 3. 由于数据包的不确定性,在一款器件的每次RF接收测试期间,测试仪不知道每个包会在哪个测试循环中传输,包的类型是什么,或者包的类型是否符合预期。

马上能看出,测试程序不能在数字测试模式中采用固定循环周期的选通隔离所需I/Q数据。同样,对同步或头的数字匹配回路不能以DigRF速度,足够快地通过ATE仪器的流水线,仪器也不能完成对头信息的实时识别和决策。

- 3G手机的电源管理的设计趋势(06-15)

- 多模3G手机的前端电路设计(11-17)

- 近半3G用户选择“移动钱包” 电话支付方兴未艾(01-22)

- 基于3G手机的视频监控系统的设计方案(04-29)

- 3G手机电源管理的设计方案(05-04)

- 3G手机中的电源管理分割探讨(05-27)