多媒体应用处理器效能强化关键

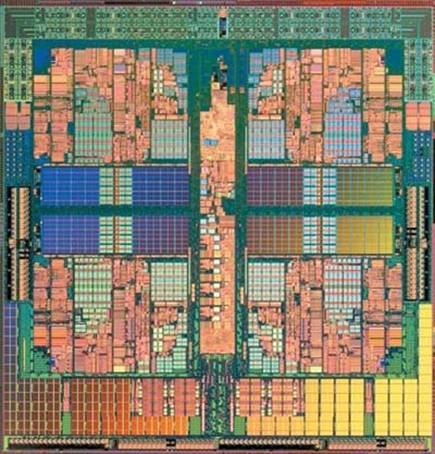

图说:行动终端装置应用愈来愈丰富,但系统能应用的资源却相对有限,如何让装置展现最佳多媒体呈现效果?处理器架构与效能绝对是重要关键!时下如PDA、PMP、PND…都需要极高运算效能支持,架构最佳化多媒体应用处理器与系统环境,已是这类行动装置实用价值的重要基础…

手机、数字电视、数字相机、个人导航装置(PND)、可携式播放机(PMP)…等,处理原本主要用途的组件,称为基频处理器(Baseband Processor),不过在多媒体运用,特别是愈强调质量的影音播放用途,已超越基频处理器的处理能力,因此,多媒体应用处理器(Multimedia Application Processor),成为行动装置中协同处理器一员。

换言之,多媒体应用处理器原本只是行动装置内众多处理器的1种,以手机为例,内部处理器根据IDC定义,有高阶多媒体应用处理器(High-End Multimedia Application Processor)、基频或整合式基频处理器(Integrated Baseband Processor)、操作系统应用处理器(OS Application Processor)、多媒体应用处理器(Multimedia Applications Processor)、多媒体协同处理器(Multimedia Co-processor)、相机影像协同处理器(Camera Coprocessor)、及LCD屏幕控制器(LCD Controller)…等7种。

上述众处理器中,现今多媒体应用无论质与量都与时俱进的市场趋势,多媒体应用处理器在许多原本并非职司此道的行动装置上,反成了重要组件!其设计与发展趋势足以影响行动装置整体表现。

高质量多媒体应用渐多 多媒体应用处理器强化效能

多媒体应用处理器发展迄今,第1个重要的设计方向,便是强化效能。作法分为2类,其一是在原本架构上,作更进一步加强、调校,直接的作法是提升频率,并非线性提升,更重视每频率所能带来的效率(如MIPS或DMIPS/MHz),所以,微架构调整也相当重要。

多媒体应用处理器微架构强化方向相当多,举例而言,使用更高效率超纯量管线(Super-scale Pipeline),让单一频率能执行多重指令;强化浮点运算单元(FPU),如加快单倍与双倍精准度纯量运算作业速度,并加入额外16位浮点运算数据类型转换指令,增进与嵌入型3D处理器间数据交换速度;内建多媒体处理单元(Media Processor Engine),支持SIMD运作模式,如每周期能处理8、16、32位整数与32位浮点运算数据,甚至支持混合数据类型,排除封装/解封装耗费的资源,及结构化加载/储存功能,让数据不必于演算格式与机械格式间来回转换。

在微架构外部方面,可强化与内存间存取效率,如加大快取容量/频宽、降低迟延,解决L1/L2快取间的一致性问题,例如,设立1个侦测控制单元(Snoop Control Unit;SCU)然而,任何接触内存中的关联区域存取,SCU都将进行监控,测试要求的信息是否已储存在处理器L1快取中,若信息已存于快取内,就直接传回发出要求组件,否则会利用最佳化算法,尽量使数据尽可能利用L2快取,藉此排除直接写入芯片外部内存衍生的功耗,并提高整体效能。

单核心最佳化,面临多任务处理时发生瓶颈,例如,1个行动终端可能同时进行视讯/音讯播放、导航定位、数据库搜寻、无线传输…等工作,效能再强大的单一多媒体应用处理器,往往也因此捉襟见肘,所以,多核心成最佳解决方案。不过此处必须说明,这里谈的并非基频/多媒体应用处理器封装在一起的异质多核心架构,而是多媒体应用处理器本身就采用同质多核心运作。

多核心架构带来效能提升,在软件支持环境下,利用新增指令让多核心处理器于程序执行时,动态从超纯量执行切换成执行多个并行执行绪,建立程序内执行多执行绪机制,仅双核心针对译码MPEG-2效能,就比单核心提高52%!不过,多核心真正的价值,除直接效能性提升外,更重要的是多核心处理器还能充分利用不同应用指令间的平行处理(Instruction-Level Parallelism;ILP)和执行绪阶层平行化(threading-Level Parallelism;TLP),换言之,具较高ILP与TLP应用,对于多核心架构适应力较高,效能提升幅度也会更大。

至于采多核心的负面影响,则分为硬件与软件方面。硬件方面是在寸土寸金的行动终端装置,多了1组核心,就表示多1倍晶体管,但多数应用环境中,效能却并非等比提升1倍,但目前半导体技术进步,多核设计可有程度不等的晶体管共享(如L2快取或内存逻辑控制电路共享…等),降低多核芯片尺寸与功耗。

反而软件问题比较复杂,例如,多个执行绪甚至应用程序存取同1个内存区块问题,如果,某1个程序没有针对多核心运作最佳化,可能就会让系统不稳定,因此,因应多核环境修正嵌入式软件与针对多核心最佳化,是目前推展多核心多媒体应用处理器颇大的阻碍。

不过,总体来看,就如同x86处理器在频率发展遭遇高耗能与高热瓶颈后,即透过多核心抒解的发展轨迹,多媒体应用处理器采多核心抒解性能瓶颈,也是必然趋势,不过多核心对于芯片面积更为敏感,因此,半导体制程进展成为开发关键。此外,多核心架构的省电机制设计也相当重要,如果分配得宜,能比单核心更省电、且效能更高。

- Xilleon 240单芯片数字电视解决方案 (04-21)

- 联通CDMA手机采用威盛处理器 打破高通垄断格局(11-19)

- 基于多媒体处理器VG2的智能家居控制器设计(02-21)

- 消费类音频应用的解决方案(02-29)

- 基于SAlll0微处理器的掌上电脑液晶显示器的设计与实现(03-08)

- 使用双处理器延长电池寿命(05-23)